“摩尔定律变成了半导体行业的使命,变成了我们每个人的使命,每个人都在谈摩尔定律。”2021年11月3日,在由AspenCore《电子工程专辑》、《国际电子商情》和《电子技术设计》主办的“2021全球双峰会”上,Cadence公司全球副总裁、亚太区及日本地区总裁石丰瑜先生以“持续推进摩尔时代的IC设计艺术”为题,介绍了摩尔定律时代芯片设计企业面临的巨大压力,以及如何利用创新的EDA工具迎接摩尔定律挑战。

Cadence公司全球副总裁、亚太区及日本地区总裁石丰瑜先生

演讲开始,石丰瑜先生分享了疫情隔离期间对人生和人类的一些思考。两百年前的人,跟二十万年前的人生活上有什么差别?说实话,没啥差别,可能只是所用工具的种类稍微多了一点;二十万年前的人类跟两万年前的人相比,生活上有什么差别?两万年前的人开始画画了,开始祭祀、追思自己的祖先;两万年前的人类跟两千年前的人类相比呢?两千年前开始有农业、文字,开始有一些艺术上更精美的创作;两千年前跟两百年前的人类相比呢?两百年前开始有工业革命了;两百年前的人类跟二十年前的人类相比,差距已经无法想象了。二十年前还没有智能手机,连支付宝跟微信支付都用不了。石丰瑜先生问:“两百万年前、二十万年前、两百年前、二十年前、两年前,以及未来,这个世界会变化什么样子?”

世界的发展跟Gordon Moore有关。1965年Gordon Moore提出,集成电路的发展,每18个月到每两年,在同一片芯片上,在同样成本的条件下,能塞进去的晶体管数量是原来的两倍,这就是所谓的“摩尔定律”。“严格来讲,摩尔定律不是一个定律,是观察的结果。后来,这个观察结果变成了预测,预测变成了伟大的英特尔公司的企业使命。又过了二三十年,变成了半导体行业的使命,变成了我们每个人的使命,每个人都在谈摩尔定律。”石丰瑜先生说。

由Gordon Moore提出的摩尔定律改变了世界。

从1965年到2016年,芯片中晶体管的数量增长了170亿倍,虽然这无法想象,但苹果公司M1 CPU中晶体管数量,大概就是160亿根。石丰瑜先生认为,到底是18个月翻倍还是24个月翻倍,这并不重要,重要的是它的量级反映在我们每天使用的产品上。过去这些年来的快速发展,很大一部分原因是摩尔定律。

几年前开始,很多人都在问,摩尔定律是不是走不下去了?是不是要撞到墙了?是不是大家开始没办法跟上它的脚步了?

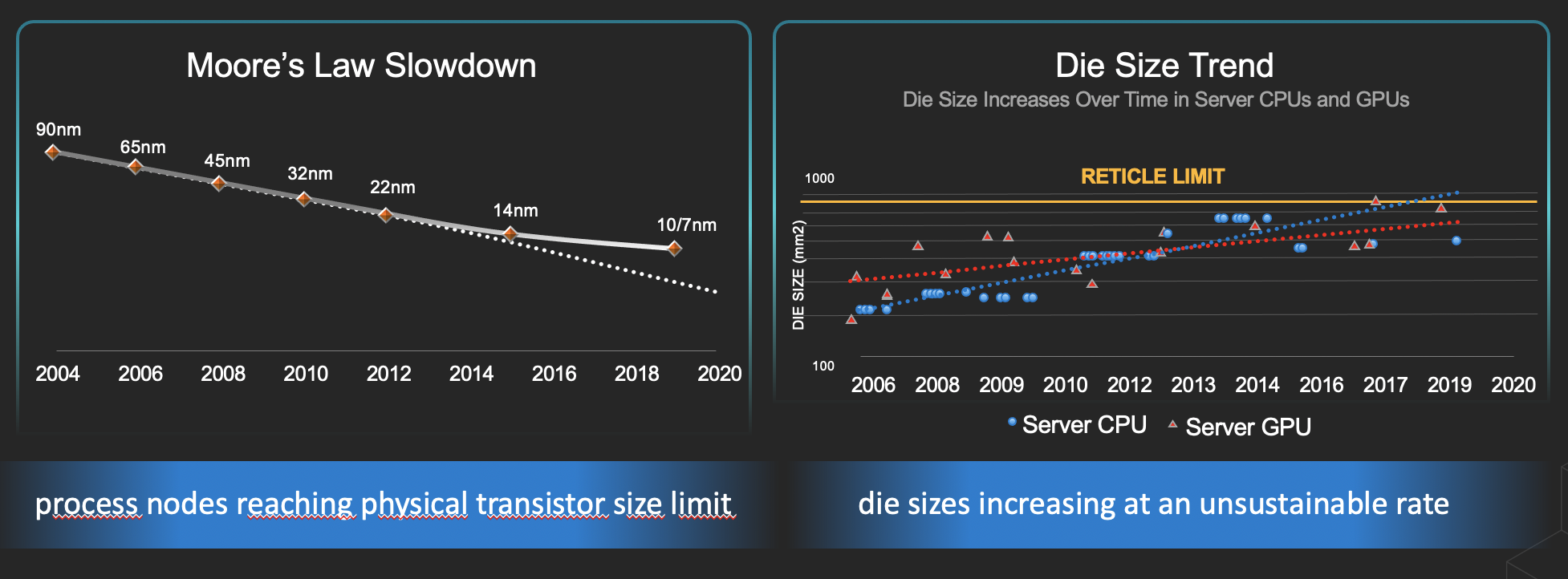

一些真实的数据表明摩尔定律的发展的确越来越艰难。每一个节点依次上量的时间点,由原来每两年有一个节点,到14nm开始变慢了,10nm、7nm就更慢了。

摩尔定律演进速度减缓,芯片面积趋近光罩极限

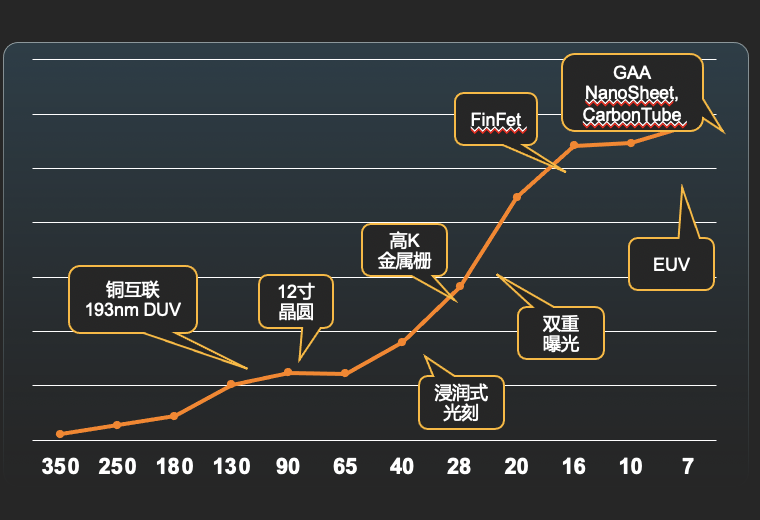

“为什么会越走越慢?我们来看看这几年来遇到了什么问题。”石丰瑜先生说,以前绝大多数是工程上的问题,努力一下就能解决。接下来会遇到物理上的问题。芯片越做越小,塞的晶体管越来越多,用铝布线会产生电子迁移的问题,芯片用不了几年就会坏。另外还会遇到光刻机的问题,原来用的光刻机光源不够细,要改成193nm的,半导体制程工艺必须从铝改成铜,这对制造工艺来讲是巨大的挑战。整个构造中有一些透镜和光学系统,193nm的光源到45nm就没办法再微缩下去了;使用浸润式光刻可以将45nm微缩到28nm;然后又遇到了问题,开始漏电,所以只能换材料。中间的绝缘层要全部换掉,需要解决物理和制程上的挑战。然而,2D解决不了漏电问题,便出现了FinFet技术,晶体管的构架变成了3D。为了解决光源问题,从10nm、7nm开始使用多光罩曝光,原来画一条线可以解决问题,现在光本身比线还要粗,怎么办?左边曝一次光,右边曝一次光,中间留下的细缝,刚好就是6nm,但这样的制程成本会非常高。

制程设计规则复杂度飙升

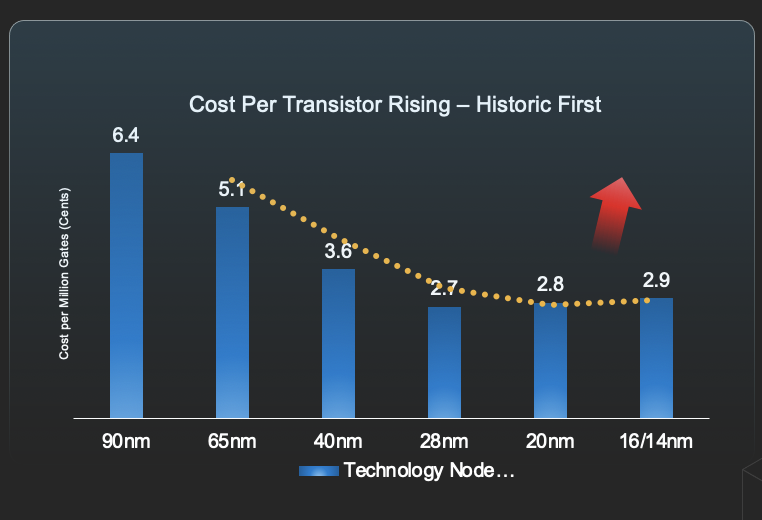

“无论是从制程的角度还是EDA编程的角度,每一个晶体管的成本都开始上升,成本触底。”石丰瑜先生说,“成本增加了,还有几家公司会用这种制程工艺?”

单个晶体管成本触底

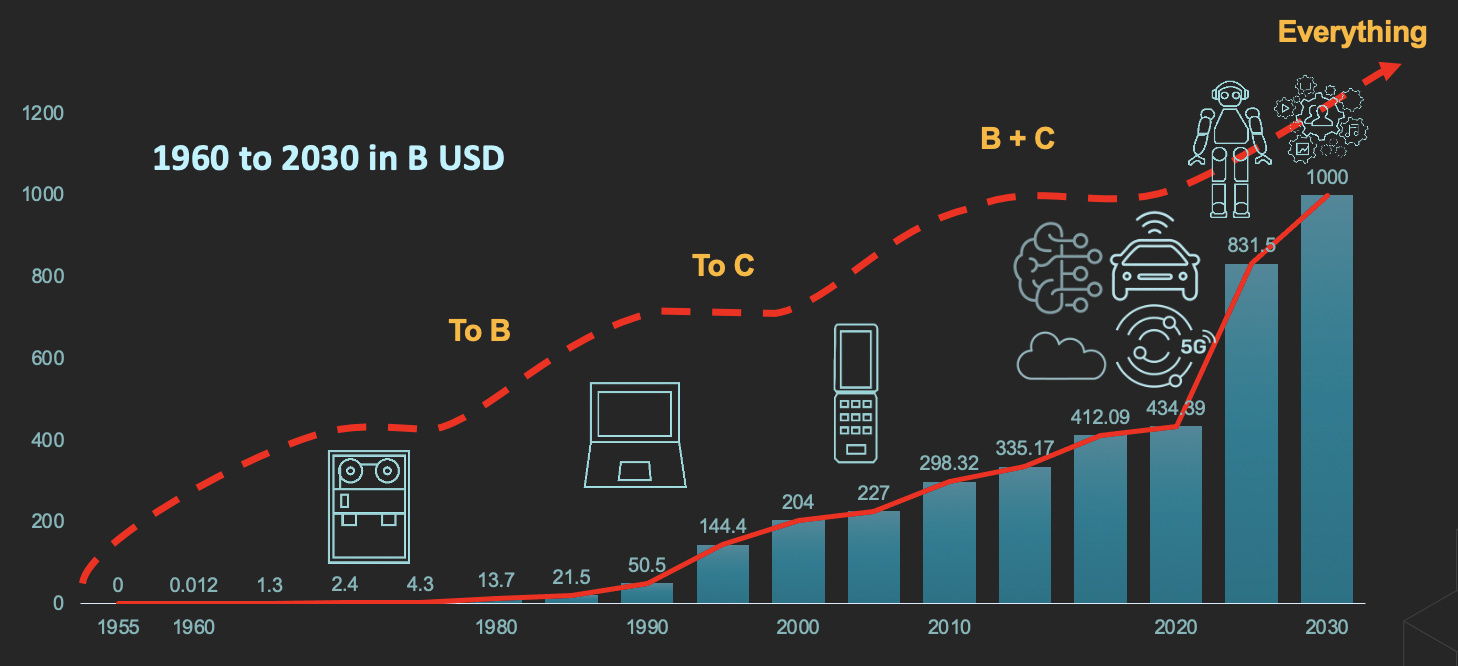

1980年代,半导体主要服务于To B市场的大型机和通信交换机;90年代开始,To C出现了,PC机也出现了,逐渐有了一些量级。一旦有了数量,就能够摊去非常高的研发成本;2016年后,To B和To C都出现了,这时还出现了云。 “大家想想数据中心需要多少半导体?一个4G/5G的基站,需要多少的半导体?”石丰瑜先生说,手机和终端带来了另一波的增长。根据预测,2020年到2030年,半导体的产值很可能会从5000亿美金变成10000亿美金。2030年后或许不是To B或To C了,而是万物互联,所有的东西都需要半导体。“人类对美好生活的向往与需求延续着摩尔定律”。

人类对美好生活的追求,延续着“摩尔定律”的生命

延续摩尔定律要靠光刻、新材料,或者比较梦幻的构架。因此芯片设计厂商、EDA公司、晶圆厂必须紧密合作,从合作中萃取更多价值,将摩尔定律再往前推进一、两代。

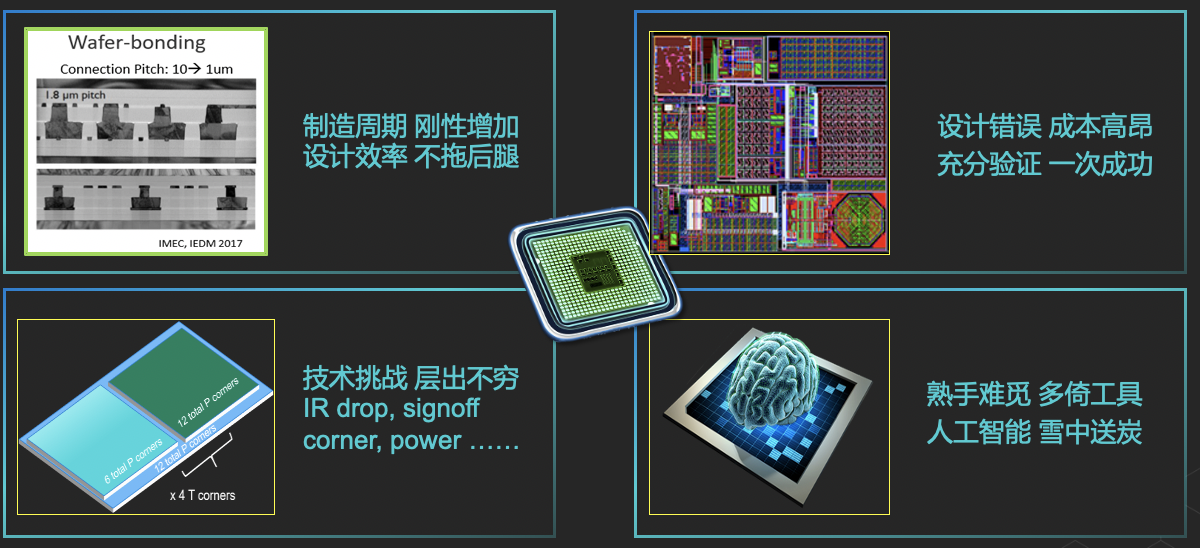

在摩尔定律时代,芯片设计企业面临巨大的压力,制造周期越来越长,设计效率越来越高,哪怕犯一个错误,代价也非常高昂。石丰瑜先生举例说,一颗芯片送到晶圆厂生产需要四五个月,如果回来发现有bug,修复后再送去,又需要四五个月。

摩尔定律时代,芯片设计公司面临巨大的压力

石丰瑜先生说,从前功耗讲的就是晶体管本身的功耗,其他的功耗都不是问题。现在内部功耗占49%;拉线越做越细,越拉越长,阻抗越来越高,功耗也占到了49%。拉线决定了一颗芯片的功耗,也即热表现。

GPU/CPU中有一种新的功耗,叫Glitch power,7nm为20%,5nm为30%。这个问题只能让工具来解决,人是解决不了的。不能等芯片设计完了才知道有问题,在写RTL的时候就要知道问题的存在,并马上修正。“RTL怎么可能马上看到功耗?”石丰瑜先生说,“这不是一个工具能够解决的问题,而需要利用一系列工具来解决。”

在芯片设计人员紧缺的情况下,一种可行的解决办法是利用工具替代人。如果一个人原来只用一套工具,那么现在可以让一个人使用三套工具。“Cadence可以帮助你选择正确的方法,采用正确的流程。”

人工智能是设计行业面临的挑战和机遇。例如做仿真的时候,如果最后一刻有个小问题要修改,利用人工智能进行分析,就可以跳过跟修改无关的工作,从而节省一半以上的时间,并能达到同样的覆盖率。

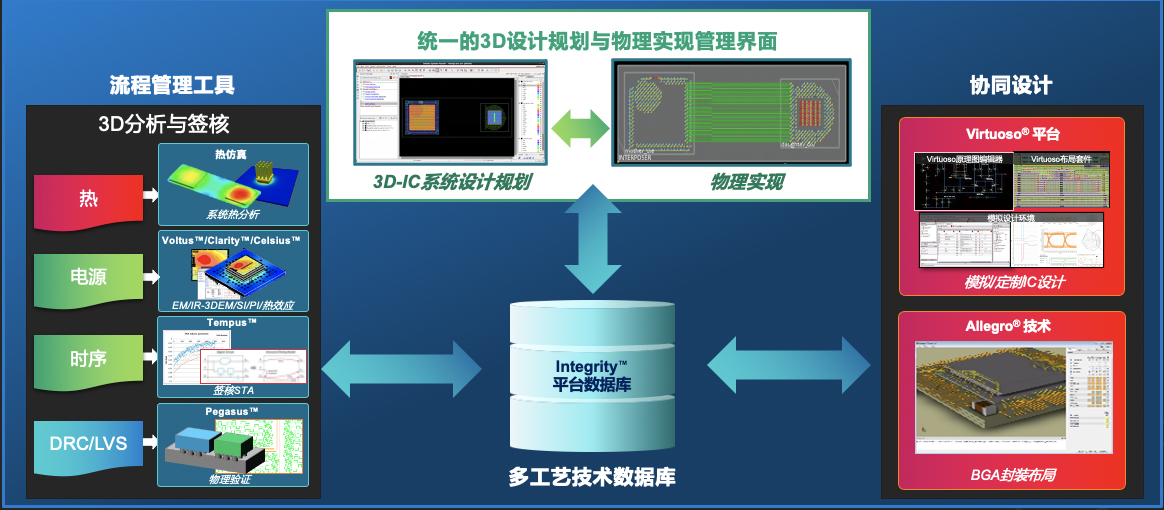

石丰瑜先生还提到,2.5/3D IC技术以更短的引线、更低的功耗、更高的性能、更高的带宽、更小的封装尺寸和更小的良率来延续摩尔定律。

Cadence的Integrity 3D-IC平台

演讲的最后,石丰瑜先生介绍说,Cadence的Integrity 3D-IC平台是业界首个集成化、高容量3D平台,可在单个统一的用户管理界面中进行3D设计规划、物理实现和系统分析。“Cadence是现在全世界唯一一家有数字工具、模拟工具、PCB工具的EDA公司,两年前开始我们正式推出系统工具,要算热、电磁波都可以。我们搭了这样一个平台,让所有这些不同的工具未来有同一个数据库/界面,设计人员可以在同一个界面里互相调用工具,在还不需要流片之前就能找到问题,把芯片设计出来。”

最前沿的电子设计资讯

最前沿的电子设计资讯