DDR4信号参考电源层,阻抗会有影响吗?

按照上面两种情况做出来的阻抗条,实际测试出来的阻抗是一样的吗?哪个会偏高?为什么?

这个问题一开始出现的时候其实我们和大多数铁杆的想法是一样的,甚至很坚持的认为阻抗只与它的上下参考平面的距离相关,可以直接用“达达”的回复来表达我们的说法,直到我们遇到真实的情况去测试的时候才发现,为什么阻抗会和我们计算的阻抗有偏差呢?所以才有了这篇文章。

从大家的回答来看我们也很欣慰,部分铁杆跟着我们一起学习,居然达到了某种程度的登峰造极,道法开始变得深不可测了,居然没有难倒你们。这其中离不开阻抗最本质的理解,那就是近似的认为Z=(L/C)^1/2,这么理解来看的话,阻抗确实就和回流有很大关系了。我们上面说的阻抗和到其参考平面的距离成正比,虽然上面的电源层离线路最近,但从回流的角度看,电源层还不是信号的直接回流路径,会使得回流路径或多或少的变长,环路变大,导致阻抗也跟着变大,这个是最直接的影响。

这其中又会有阻抗Coupon条和实际板子之间的差异,在这种非常规的设计上,Coupon条通常不会根据板子的实际情况来制作,比如实际情况信号上面一层是电源层,而下面一层是地,但在Coupon条上会把上下两层都当成是平面层,因为Coupon条上是不会有电源层的;另外就算Coupon层上有电源层,这个电源层也是一个浮铜层,它没法像实际情况那样通过电容等回流到地,所以这种情况的阻抗和我们实际上信号真实的阻抗还是有点区别。

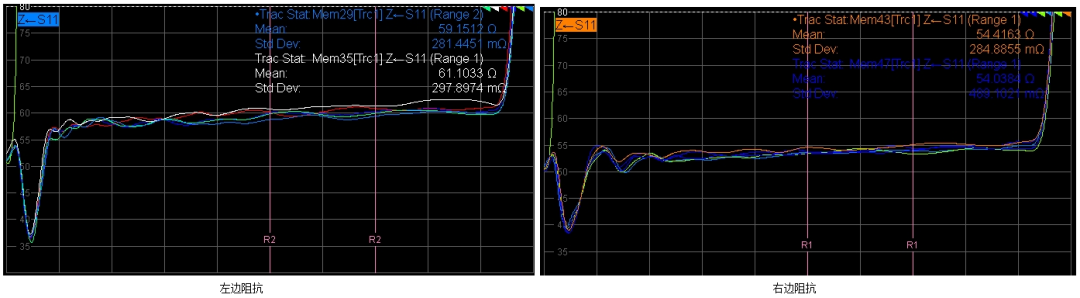

简单总结一下这个问题的答案就是,从Coupon条来看,左边线路的阻抗确实会比右边线路的阻抗测出来的要高,下面是我们测试出来的一个

阻抗结果。但实际板内的情况又是什么呢?卖个关子,这个问题还没完,请继续看后面我们深层次的分析。

(以下内容选自部分网友答题)

应该来说对信号影响最主要还是靠的最近的一层,基本远距离的两层GND没有大的影响,但是DDR4这种上下参考层中一层是power对工程来说是OK的,和上下都是GND差别不大

@ moody

评分:2分

不一样,左图的阻抗大一些吧。回流路径大,H也大了。。。实际测试时参考地端的选取也会有影响

@ 杆

评分:3分

不一样。左边的偏高。因为从回流的角度看,左边上面参考电源层,回流会比参考地层远,多了从电源层到地层的路径。

@ 涌

评分:3分

秋风起,银杏黄,香山红。身在江南大都市上海的阿豹想在本周末去北京看深秋的香山红叶,登层林尽染的八达长城。坐上火车半天功夫就到了,一天游遍北京。可在京朋友告诉他这两个景点相距挺远的,力邀晚上一聚,明天再玩另一个。豹想咋?沪距京1.2千公里,说明沪到京任何地方都是1.2才对呀。旁边的虎课长表扬阿豹,小伙子数学思维挺好的嘛,1K+1=1K。分两种情况:1.信号感受到的阻抗。参考电源和参考地阻抗一样,因为电源和地之间的阻抗为几十毫R,相对信号50或100R,毛毛雨还没滴下,信号已溜达很远了。2.测试员看到的阻抗,当选取信号脚和地脚在一起时,参考电源和参考地的阻抗一样。当选取信号脚和地脚相距甚远,或随意选取时,参考电源比参考地的阻抗大一些。

@ 山水江南

评分:3分

很明显,无论只要与信号线重叠的平面导体,就构成了参考平面,不管他是GND还是VCC,影响信号线阻抗大小只有:1.走线宽度;2.介质厚度;3介电常数;4,铜箔的厚度,这个SI9000里面已经很明显了

@ 达达

评分:2分

不一样的。内层不与地层相连的回流地孔的方式的特性阻抗略高一点。信号原本是参考地层的,换层后却参考了电源,相当于回流路径更远,截面积更大,分布电感也更大。理想条件下:阻抗=L/C的0.5次方。可见L和阻抗是正比关系。L大,阻抗大。

@ 欧阳

评分:3分

实际电路板中,电源和地之间有de-cap和vrm cap,可以认为高频是联通的。这个和你的test coupon不同

@ 刘大昭

评分:3分

不一样。相临层都为地网络的偏低。其信号回流截面积要小,寄生的电感小,所以特性阻抗也小。公式:Z=(L/C)^1/2

@ Ben

评分:3分

如果信号回流是以Ground为参考,那么参考电源层的会有一部分通过Power和Ground间的耦合电容或者芯片周围的Decap作为回流,回流路径变大,对应的电感L会变大,导致阻抗偏高。另外信号既参考Power又参考Ground,Power和Ground形成的平面谐振腔,信号走在腔体中间,会受谐振频率的影响,导致插损会有谐振出现。

@ 穆

评分:3分

个人认为应该TDR测试的阻抗是一样的,参考电源只是影响到回流路径,对阻抗应该没 影响

@ Alan

评分:2分

结论是第一种参考电源层阻抗大;

理由是参考电源层的特征阻抗比参考地层的特征阻抗多了一个电源层到地层的阻抗;

Zpwr=Z12+Z23

Zgnd=Z12

Z12为信号到电源层阻抗,Z23为电源层到地层阻抗;

平面间阻抗计算:

(Z23=377*h/w*√εr)

Z23表示电源层到地层阻抗

h表示平面间的介质厚度

w表示平面的宽度

εr表示平面间材料的介电常数

@ 起风了

评分:3分

理论上讲的话,肯定GND做参考对带状线有阻抗降低的影响, 实际经验看的话,对信号影响最主要还是靠的最近的一层,基本远距离的两层GND没有大的影响。

@ 天将降大任于我

评分:3分

不一样。个人认为是地孔不与信号上层平面接触的情况阻抗会偏高一点,因为在根据带状线阻抗计算公式,相当于增加了H,所以会偏大一点。

@ Jamie

评分:3分

DDR4这种上下参考层中一层是power对工程来说是OK的,和上下都是GND差别不大,因为我们就这么干过。但理论上,盲猜左边实测阻抗会比右边高。

@ 阿少

评分:3分

应该是一样的吧!高频信号的回流路径实在传输线相邻导体的正上下方,不同于直流回流路径吧!

@ Luffy

评分:2分

参考电源的会更高,因为电源到地还有距离,相当于增加了H

@ balance

评分:3分

满大街的4层板表示 尽管梭哈

PS DDR5 CPU跟DIMM中间还有大电源层连吗

@ 小能猫

评分:2分

最前沿的电子设计资讯

最前沿的电子设计资讯