芯片设计的奥林匹克——ISSCC 2022我们继续高歌猛进,大陆港澳台地区论文总数突破三十大关。疫情当前,参会机制同时有现场出席与线上观摩。换言之,远在大洋彼岸的我们可以继续隔岸ISSCC的直播了。矽说小编一如既往的为大家送上前瞻!随着各种模拟大佬下海写公众号,本文就先水一水ISSCC 2022的数字芯片。最后,完整Advance Program可通过文末点击“阅读原文”获得。(感谢热心网友爬虫官网链接,目前还没官宣~)

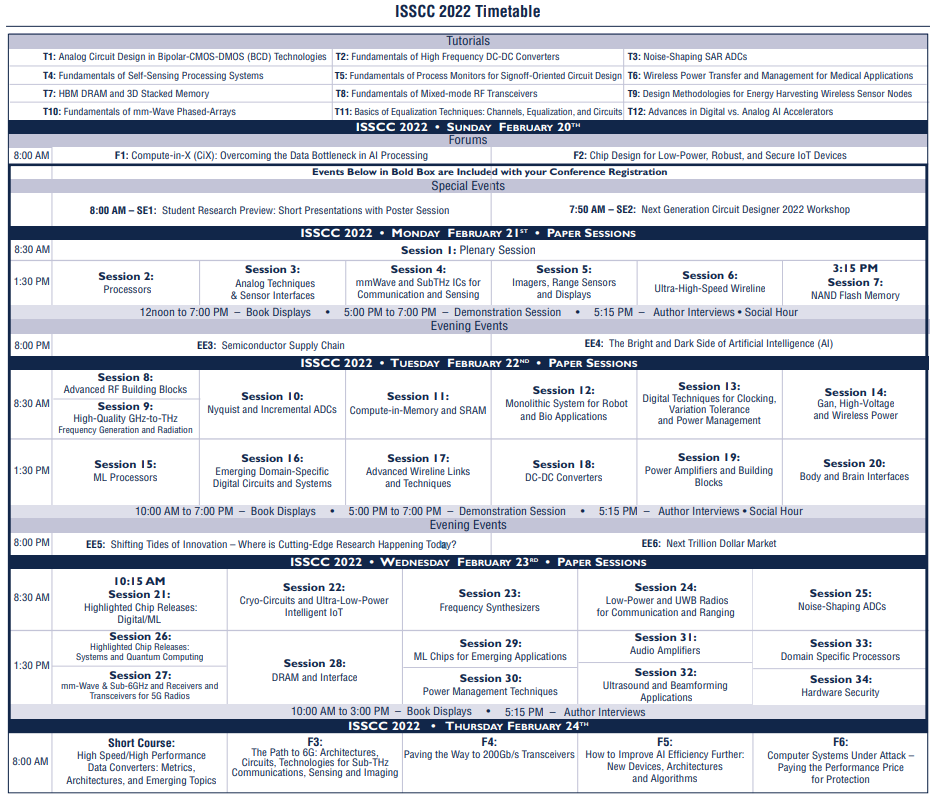

今年的ISSCC将于2022年2月20日开幕(不得不说有点2)。我们正月初一是2月1日,开会的时候早已过了元宵。很多童鞋们可能已经要开学了。新的学期可以从新的ppt看起! 议程也从去年的在线RPG会议(录视频+现场回答问题)式改回标准议程。

接下来是正文:

近年来中美的摩擦,让一种设备——光刻机进入了大众的视野,从网约车司机到居委会大妈无不谈论着EUV光刻机和7/5nm芯片。不可讳言,对于很多我国民族企业而言,由于实体名单的限制,原来芯片产业的发动机——摩尔定律指向的芯片尺寸微缩——已经实际上已经停滞了。不仅如此,随着芯片设计成本在5nm以上的激增,后摩尔的芯片技术——不依赖尺寸微缩而提高芯片性能的技术——无疑成为了当今数字电路的热宠。今年5月,我写过一篇《从ISSCC 2021看后摩尔芯片技术》。本次前瞻,让我再来看看ISSCC 2022里这些新技术的发展趋势。

忽如一夜春风来

数字存算满地开

在整个ISSCC的AP里面,题目中含有存算一体的论文高达14篇,加上近似概念的可能超过16篇。16篇的概念是什么?ISSCC 2022总共录取了200篇文章,其中82篇文章是数字类的,每5篇数字文章就有一篇是存算一体。俨然存算一体成为打破传统数字电路方法的新一类电路。ISSCC中有12个技术track里,存算一体的数量战胜了5个track的数量,可见一斑。

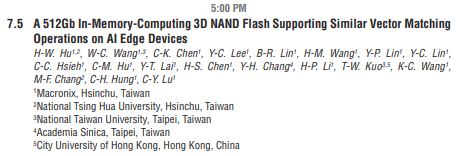

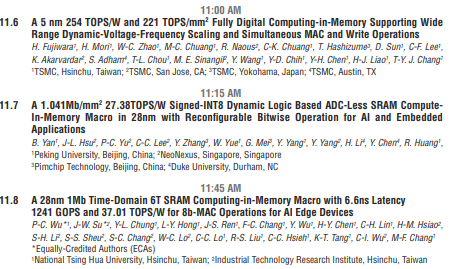

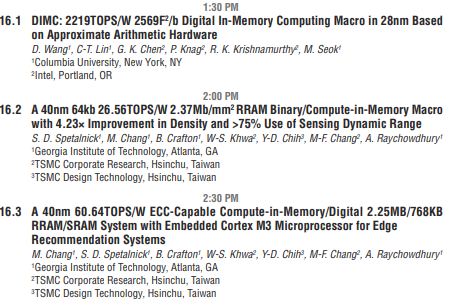

今年的存算一体具有两个特点。第一是,一切memory皆可存算,从3D Nand flash到GDDR6 DRAM,到MRAM,再有PCRAM,和传统存算赛道上的SRAM ReRAM。存算已经每一类存储器的争奇斗艳的舞台。在这个赛道上,传统存储器大厂(TSMC、三星和海力士)无疑是主角。另一个趋势是,这些存算一体已经不单纯用于整数矢量计算和乘加电路,也有其他计算范式涌现,比如匹配、浮点计算、加解密等。

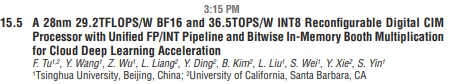

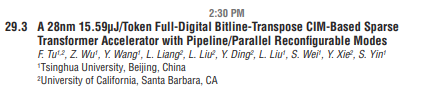

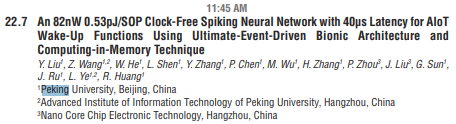

另一个特点是基于数字方法和近数字方法(时间域)开始取代了前两年大行其道的模拟计算。在ISSCC 2021上只有一篇数字存算一体,明年则大量涌现。该方法可以有效地避免模拟计算和ADC及其非理想性。在较高精度(INT8甚至是浮点)的存算一体电路的能效和模拟计算不相上下,又有很强的鲁棒性。清华大学提出了支持BF16(人工智能训练中的专用16位浮点数)的可重构数字存算一体电路,还有支持Transformer计算的存算一体系统,北京大学实现了高能效的INT8数字计算单元,摒弃了ADC,并且与ISSCC 2021的INT8模拟计算相比,效率不减反增加。

Chiplet集成芯片

一场关于维度的战争

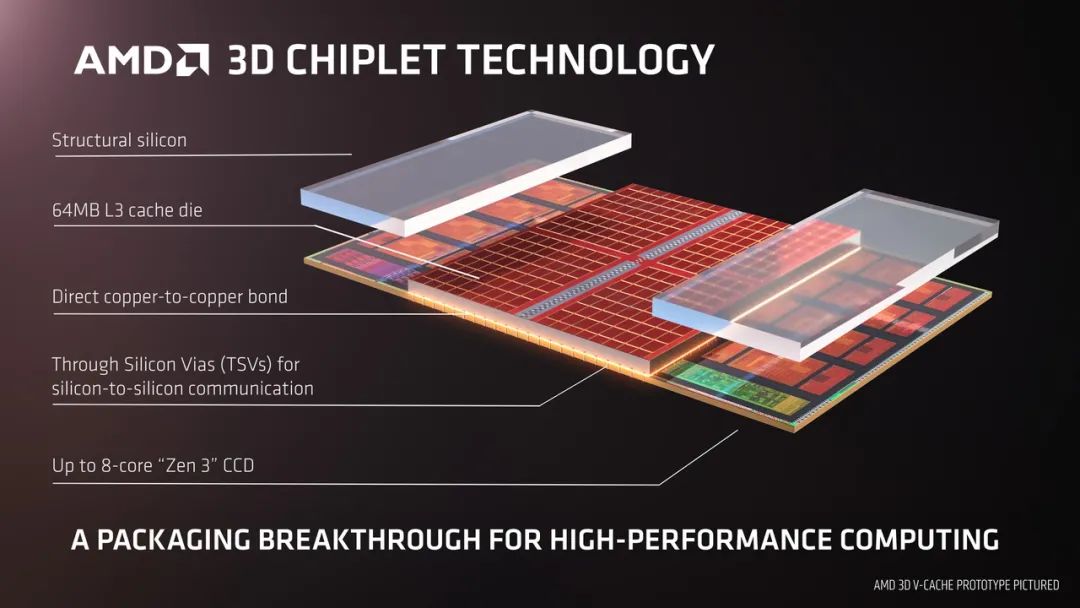

在ISSCC 2020的时候,小编写过一篇《后SoC时代或将迎来Chiplet拐点》的小散文,展望了一下chiplet大有可为的明天。经过ISSCC 2021 Chiplet的小冷静期,终于ISSCC 2022的Chiplet论文迎来了大爆发。首先是两大CPU厂今年基于Chiplet的爆款产品——Intel的Ponte Vecchio和AMD的3D-VCache(Zen3) 都在ISSCC上展示了技术细节。值得指出的是,这两款芯片都实现了真正意义上的3D芯片,从维度上超越了2.5D的CoWoS 和Fanout封装技术(采用硅inerposer或者RDL外沿层技术实现多层平面互连)。

通过3D堆叠,互连维度由线上升到面,从水平长距离到垂直短距离,从更高维度地去挑战冯诺依瓶颈。在实测数据中,AMD 的3D芯片效率较传统monolithic可以实现几乎一代的工艺红利。也让Chiplet集成芯片成为了除了尺寸微缩外,一条完整的新路径。

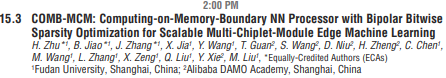

在集成芯片的探索上,国人也有不少成果的工作。阿里达摩院也实现了基于Hybrid Bonding的近存计算引擎,可用于推荐系统。复旦大学提出了面向2.5D封装的可扩展存算一体架构,通过Chiplet技术,达到流片后的再度灵活配置特性,支持不同尺度的终端学习场景。

Chiplet的发展,一个关键就是解决芯粒间高带宽的片间互连。该方案主要包含两种技术路线:1)线数少单线速度高的 Serdes路线 (适合互连制造精度较低的MCM SiP基板等较为传统的封装),相比于传统Serdes,其技术优势在于超短距离,互连信道可控,插损小,模拟射频前端电路的复杂度相对较低。ISSCC 2022上,基于PAM-4的Serdes已经实现了113Gpbs的单线速度。

2)高密度高能效的并行路线,主要用于在较为精密的硅interposer上与HBM的互连。该路线通过并行几千甚至上万根线的并行达到高带宽,相比于Serdes其能效往往可以控制在0.5pJ/bit以下(Serdes目测超过1pJ/bit)。目前,已经试产的产品中采用最先进的HBM3互连的单线速度在6.4Gbps/pin,从ISSCC 2022相关的论文看 未来HBM4单线速度应该会上看10Gbps/pin了。

另外,ISSCC 2022上也有基于3D堆叠的非数字芯片,包括多通道纳机电、能量转换芯片以及背照式TOF传感器。可见3D的降维打击不仅限于高性能处理器芯片的存储墙,实现真正意义上的异质集成将推动整个后摩尔技术的发展。

最后,感恩节祝福大家节日快乐。Black Friday的礼物就是通过下方点击“阅读原文”后,通过浏览器打开,获得完整AP,以飨广大读者。

最前沿的电子设计资讯

最前沿的电子设计资讯