前两天参加一个在线的会议,听到了Photonic bump这个新词汇,比较有意思。这里收集下相关的资料,供大家参考。

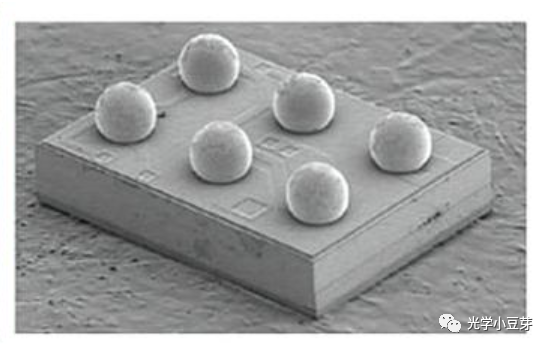

Bump的概念来源于电芯片的封装。在Flip-chip工艺中,在两颗芯片需要互联的pad区域生长出金属凸点bump,进而进行芯片的焊接,如下图所示。

(图片来自https://www.pianshen.com/article/63311198118/)

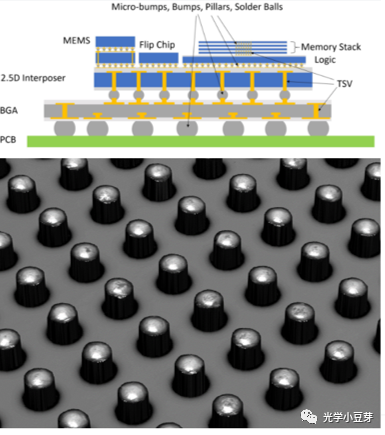

三维的示意图如下图所示,bump提供了两块芯片间电信号互联的通道。

(图片来自https://www.cyberoptics.com/cyberoptics-to-present-technical-paper-fast-100-wafer-bump-metrology-and-inspection-at-virtual-ieee-paine-conference/)

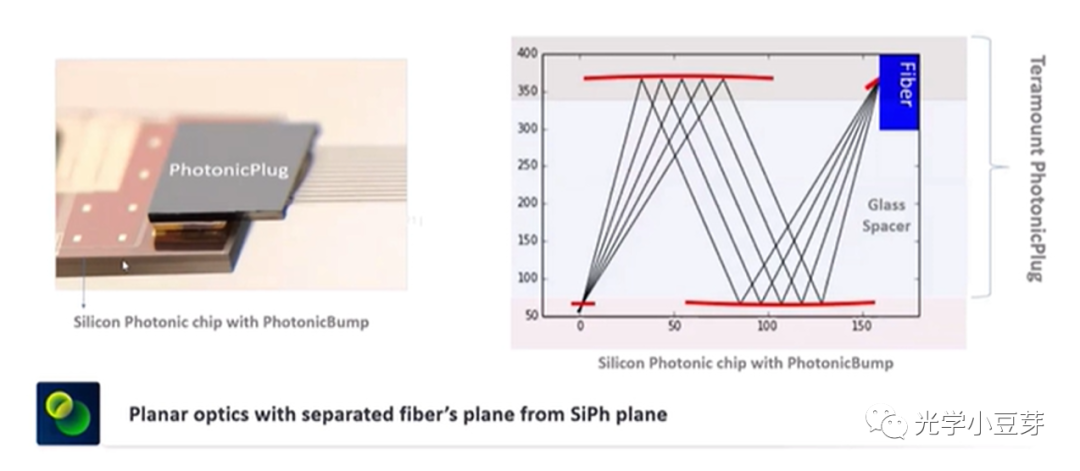

以色列创业公司Teramount提出了photonic bump的概念,作为硅光芯片和光纤连接的桥梁,避免了光纤直接与光芯片耦合的高精度对准要求,如下图所示,

Photonic bump主要由glass spacer, silicon die两部分构成,如下图所示。在顶端的硅片上加工出反射镜,在硅光芯片也需要加工出类似的反射镜,硅波导中的光经过多次反射,传输到光纤的端口。

(图片来自文献1)

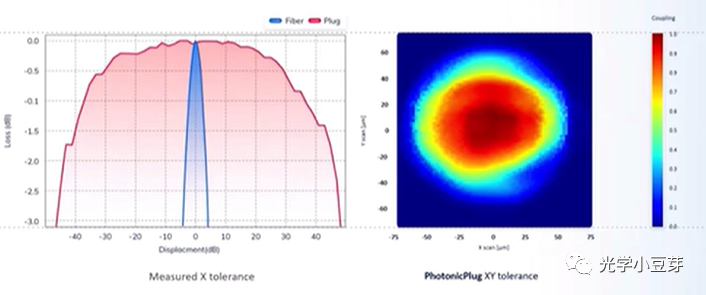

由于光纤不是直接和硅光波导耦合,光束通过多次反射,使得其对准的1dB容差高达40um,如下图所示。由于这些反射镜是在wafer上直接加工出来的,其位置的准确性由光刻精度保证。Teramount将此称为“self-aligned optics”。该方法的优势是将复杂的、精度要求高的光学assembly转移到芯片的加工上。

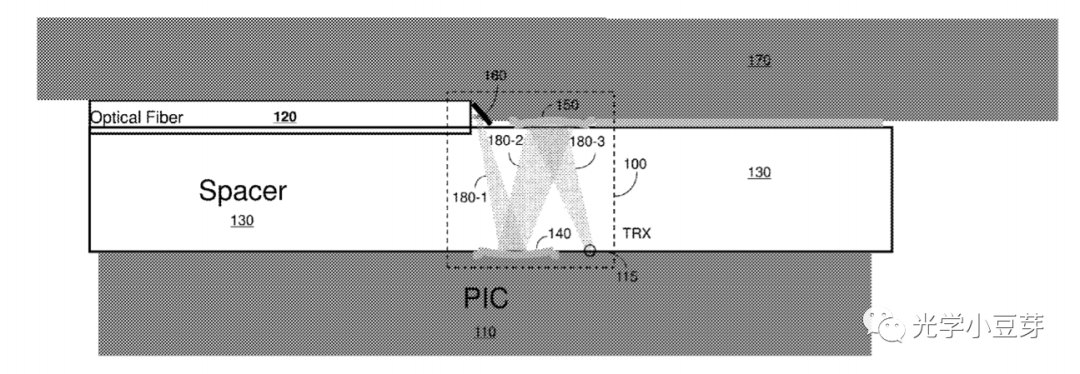

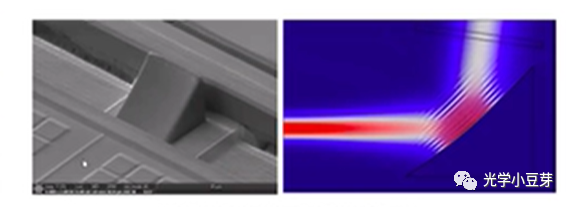

对于端面耦合器,需要额外加工一个硅棱镜,用于将光的传播方向从水平转变为竖直方向,如下图所示。基于此,还可以实现端面耦合器的wafer-level测试。

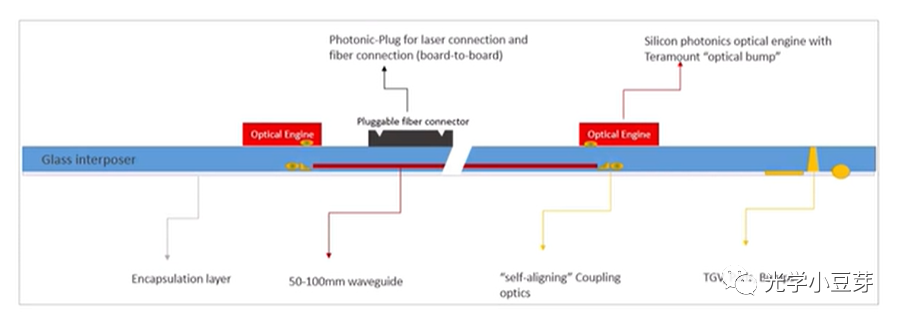

Photonic bump技术可以与传统的bump,加工在同一个interposer上,如下图所示。图中最右侧为TGV和bump, 而红色的photonic engine可以通过photonic bump实现光信号的互联,比较有意思。

简单整理下,photonic bump技术主要是通过在硅片上加工出反射镜,并结合SiO2的interposer, 实现高容差的光耦合。其难点在于硅反射镜的加工,虽然Teramount在报告中声称只额外增加了一步光刻和一步刻蚀,与现有工艺完全兼容。但是其bump的尺寸较大,并且是一个3维结构,难度也是不小的。另外,报告中并没有展示该photonic bump的耦合效率,有待进一步的报道。与之相关的photonic wire bonding的技术(光学引线键合技术 (photonic wire bonding)),小豆芽之前也介绍过。两者的区别也正是wire bonding和bump的区别,photonic wire bonding更适用于端面耦合器,而photonic bump则没有此限制,可以放置在芯片中的任意位置。两者都是硅光芯片之外做文章,增加一些额外的工艺步骤与器件来降低硅光封装的复杂性。

文章中如果有任何错误和不严谨之处,还望大家不吝指出,欢迎大家留言讨论。也欢迎大家向我提问,小豆芽会尽自己的能力给出解释。目前三个微信群都已经满员,大家有问题需要讨论的话,可以直接添加我的个人微信photon_walker。

参考文献:

1. A. Israel, et.al., "fiber to chip optical coupler", US patent 14/878,591

<script nonce="1667914696" type="text/javascript"> var first_sceen__time = (+new Date()); if ("" == 1 && document.getElementById('js_content')) { document.getElementById('js_content').addEventListener("selectstart",function(e){ e.preventDefault(); }); } </script>

最前沿的电子设计资讯

最前沿的电子设计资讯

发送给作者