Intel最近报道了其与Ayar Labs的最新合作成果,他们使用FPGA与硅光芯片构成optical IO链路,首次验证了5.12Tbps带宽的信号互联。这篇笔记主要对这一进展做些介绍。

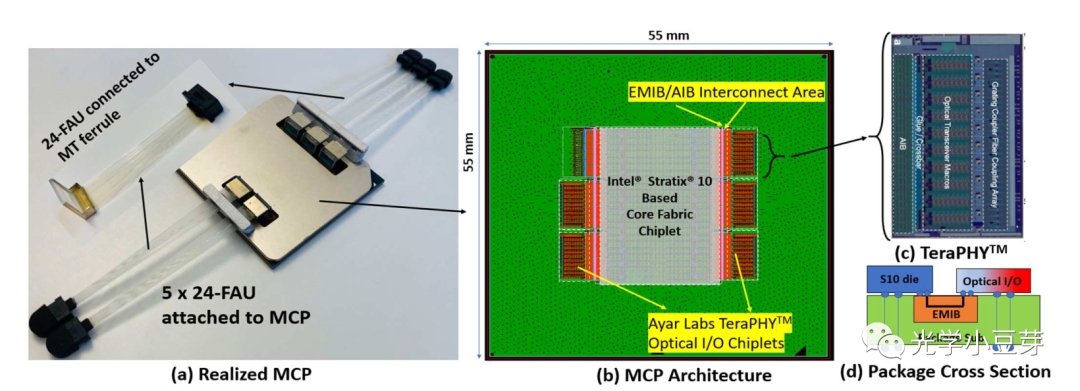

研究人员将Intel的一颗Stratix10 FPGA芯片与Ayar Labs的五颗TeraPHY封装在一起,两者都放置在衬底上,通过EMIB技术进行互联,如下图所示,

(图片来自文献1)

关于Ayar Labs的TeraPHY, 小豆芽的这篇笔记有相关介绍(OFC 2021: Ayar Labs实现1Tbps无差错的光芯片间信号互联),这里不再赘述。单颗TeraPHY芯片包含8个macro, 每个macro含8个波长的信号,每个波长的信号速率为16Gbps, 单颗TeraPHY可实现1Tbps(16Gbps*8*8)的单向信号传输,误码率低于1e-12。

将这五颗芯片封装一起,形成所谓的MCP(muli-chip package), 其工艺比单颗光芯片的封装要复杂得多,主要涉及以下工艺步骤:芯片减薄、切割(singulation)、贴片、底部填充(underfil)和光纤的粘接(fiber attach)。在芯片组装的过程中,可能会出现芯片崩边(chipping)的情况。因此需要对芯片的厚度进行优化,underfil工艺也要因为电芯片与光芯片的厚度差而进行优化。

每个TeraPHY芯片含有一个24端口的光纤阵列,整个MCP共含有120根保偏光纤。光纤阵列的一头与光芯片相连,另一头与MT连接头相连,连接头处的插损为0.35dB。

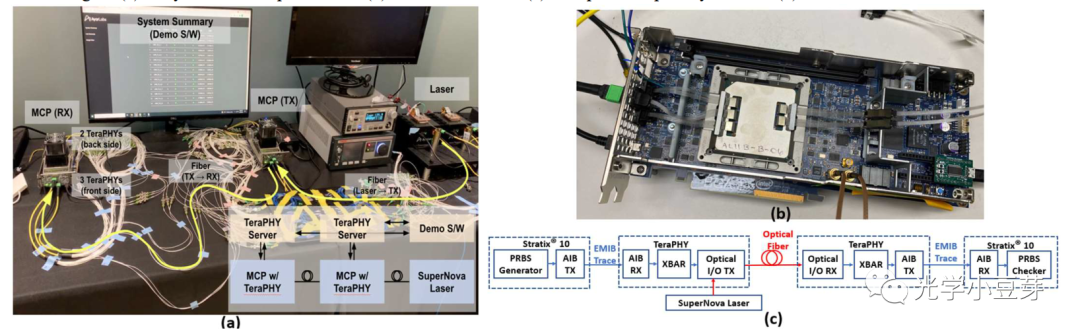

研究人员将两个MCP模块通过光纤互联,形成FPGA-TeraPHY-TeraPHY-FPGA的信号链路,如下图所示,第一个FPGA的电信号首先转换成光信号上,通过第一颗TeraPHY芯片经过光纤传递到另一颗TeraPHY上,再转换为电信号传递到第二颗FPGA芯片。

(图片来自文献1)

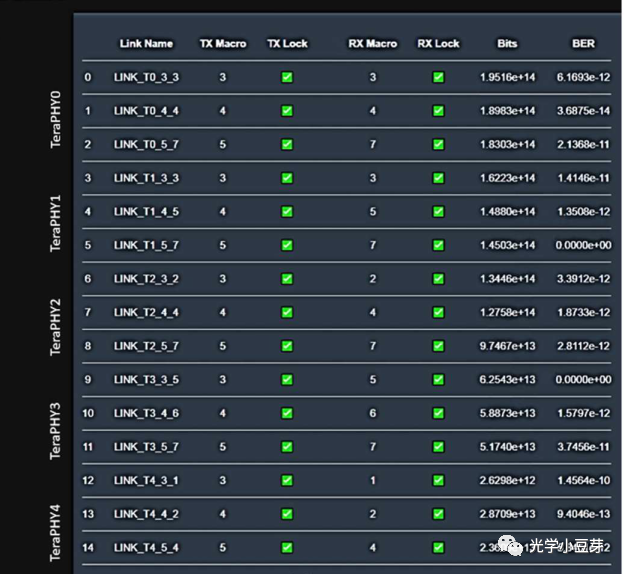

每个TeraPHY提供三个macro,用于形成15个互联的链路,对应的信号带宽为15*8*16Gbps=1.92Tbps, 这15个link的测试结果如下图所示,链路的BER都小于1e-11, 平均BER值为6.9e-12,系统的功耗为4.9-5.0pJ/bit。

(图片来自文献1)

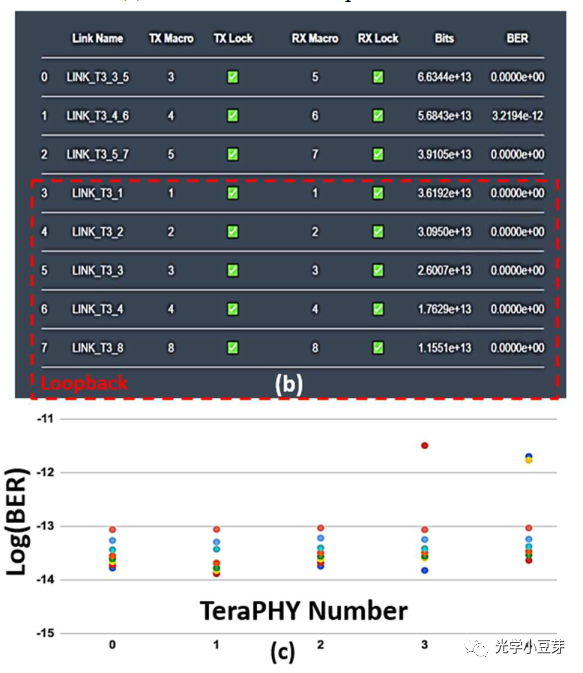

而每个TeraPHY剩余的5个maco,并未与FPGA相连,而是形成loopback的回路,这样整个系统的带宽为5.12Tbps。相应的测试结果如下图所示,链路的误码率也都在1e-11以下。

(图片来自文献1)

以上是对Intel的5.12Tbps optical IO这一进展的简单介绍,相比于OFC2021上的报道,此次报道添加了系统的实测链路数据,OFC2021上更多的是封装的热仿真结果。从Intel文章中的表述可以看出,其克服了封装上的很多工程难题,使得CPO系统可以稳定地工作。MCP中的热管理是一个技术难点,涉及到多颗芯片间的热串扰、光纤阵列粘接处的散热片处理、基于热效应的微环工作波长校准等。虽然Optical IO的概念提出了很久,但是更多的是光学链路的演示结果,Intel的该进展首次实现了FPGA-optics-FPGA链路的演示,并且误码率达到了1e-11,功耗小于5pJ/bit,是Optical IO商用化进程中的重要里程碑。

最前沿的电子设计资讯

最前沿的电子设计资讯