因为射频(RF)电路是分布参数电路,电路实际工作中容易出现集肤效应和耦合效应,所以在实际PCB设计中,会发现电路中的干扰辐射难以控制,如:数字电路与模拟电路的相互干扰、电源的噪声干扰、地线不合理造成的干扰等。正因如此,在PCB设计过程中如何权衡利弊,找到合适的折衷方案,以减少这些干扰尽可能多地,甚至避免某些电路的干扰,是RF PCB设计成败的关键。本文从PCB LAYOUT的角度,提供了一些处理技巧,对提高射频电路的抗干扰能力有很大的帮助。

1.RF布局

我们这里讨论的是多层板的元件布局。元器件布局的关键在于将元器件固定在射频路径上。通过调整其方向,使射频路径的长度最小化,输入远离输出,尽量将大功率电路和小功率电路分开。信号远离高速数字信号和射频信号。

布局中经常使用以下技术。

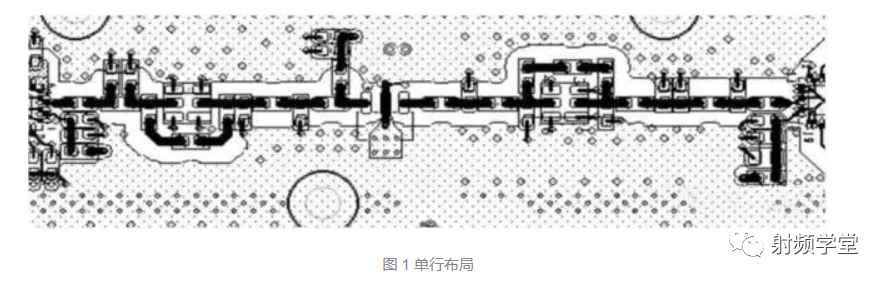

1.1 单行布局

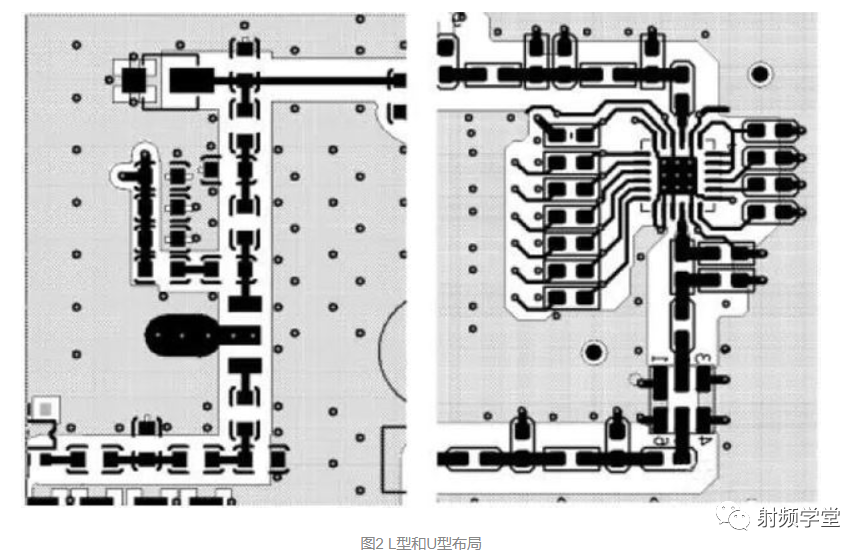

射频主信号的分量尽量直线排列,如图1所示。但由于PCB板和腔体空间的限制,很多情况下不能直线排列。这时候可以采用L型布局。最好不要使用 U 型布局(如图 2 所示)。当不可避免时,最好将输入和输出之间的距离增加到至少1.5cm。

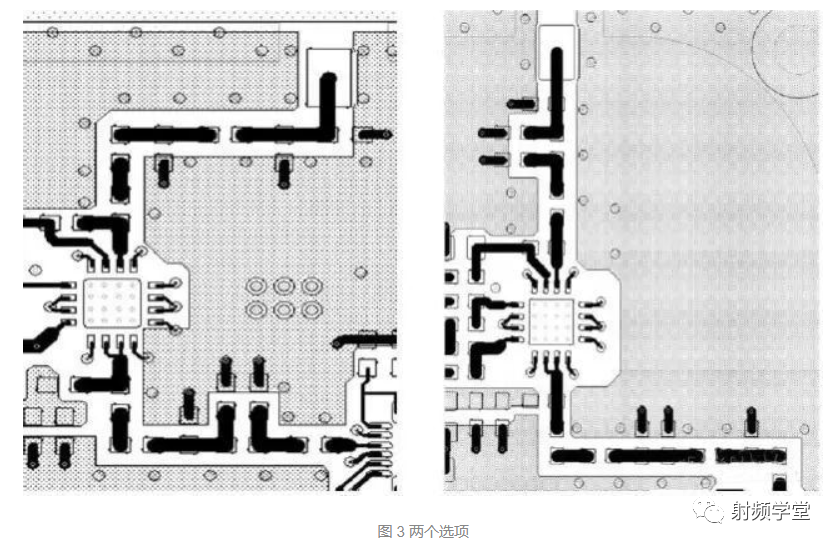

另外,在使用L型或U型布局时,拐点不要一进入界面就拐弯,如图3左图,而是稍微直线后,右图在图 3 中。

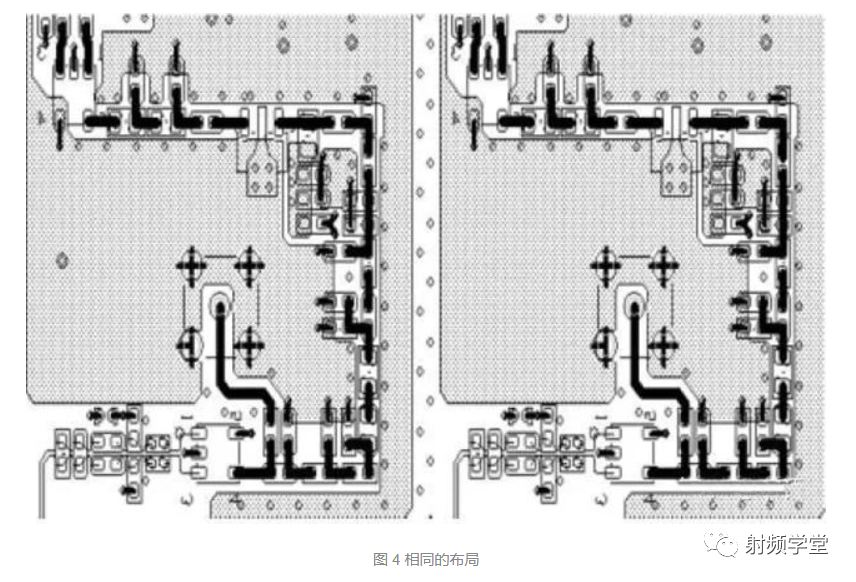

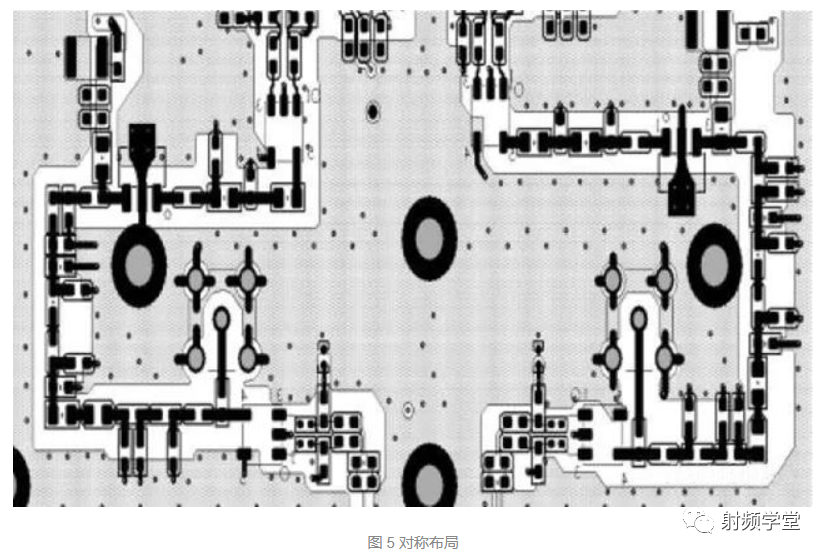

1.2 相同或对称布局

相同的模块应尽可能做成相同布局或对称布局,如图4和图5所示。

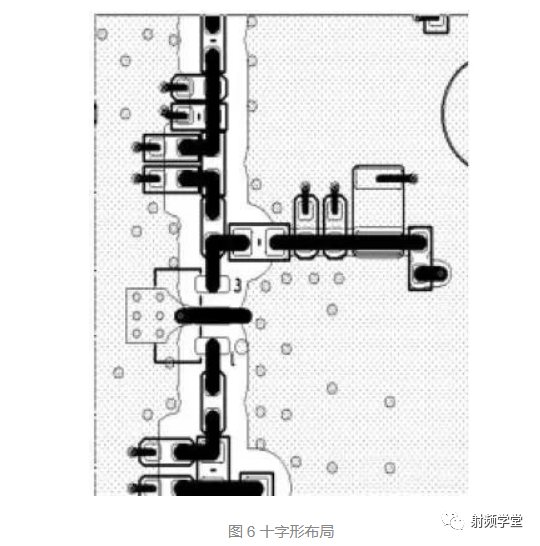

1.3 十字形布局

偏置电路的馈电电感垂直于RF通道放置,如图6所示,主要是为了避免电感器件之间的互感。

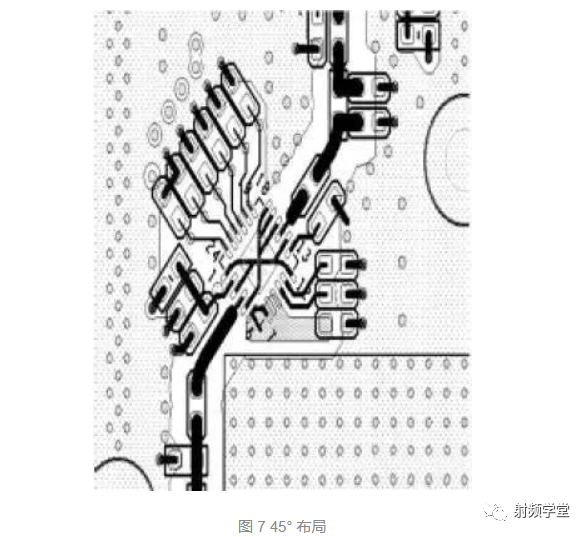

1.4 45°布局

为合理利用空间,可将器件按45度方向排列,使射频线路尽可能短,如图7所示。

2.射频布线

对布线的总体要求是:射频信号走线短而直,减少线路突变,少钻孔,不与其他信号线相交,在射频信号线周围增加尽可能多的接地过孔。

以下是一些常用的优化方法:

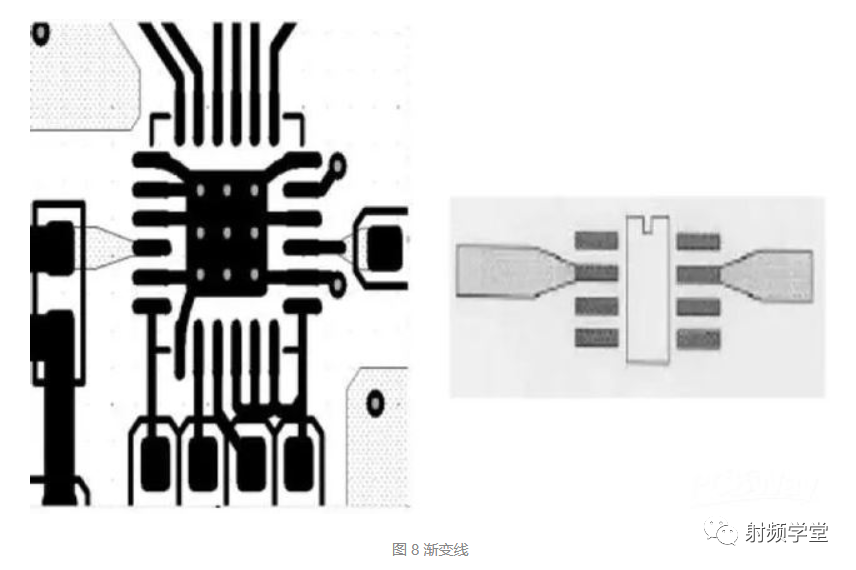

2.1 渐变线处理

在射频线宽远大于IC器件管脚宽度的情况下,接触芯片的线宽采用渐变的方式,如图8所示。

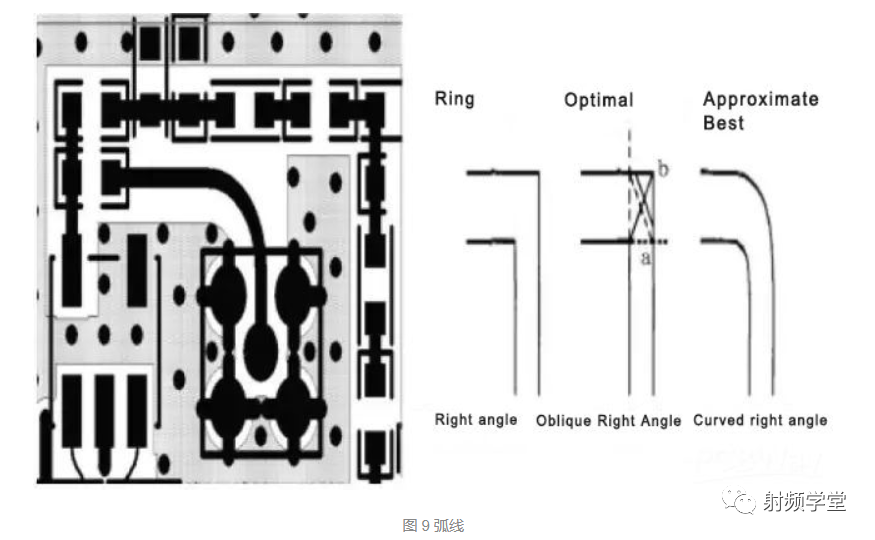

2.2 圆弧线加工

如果射频线不能笔直,则将其视为弧线,这样可以减少射频信号的外辐射和相互耦合。实验表明,将传输线的拐角弯成直角,可以最大限度地减少回波损耗。如图 9 所示。

2.3 地线和电源

地线应尽可能粗。如果可能的话,PCB的每一层都应该尽可能地接地,并且地线应该连接到主地线。应制作更多的接地过孔,以尽可能降低接地阻抗。

射频电路的电源尽量不要分平面。整个电源层不仅增加了电源层对射频信号的辐射,而且容易受到射频信号的干扰。所以电源线或平面一般采用长条形,根据电流大小进行加工。在满足当前容量的前提下尽量加厚,但不能无限加宽。处理电源线时,一定要避免环路。

电源线和地线的方向必须与射频信号的方向平行,但不能重叠。最好在有十字架的地方使用垂直十字架。

2.4 交叉处理

如果可能,RF 信号和 IF 信号应与地交叉。

当射频信号与其他信号走线交叉时,尽量沿着它们之间的射频走线布置一层与主地相连的地。如果不可能,请确保它们已交叉。这里的其他信号走线还包括电源线。

2.5 共面阻抗

射频信号、干扰源、敏感信号等重要信号的共面阻抗,既能提高信号的抗干扰能力,又能降低信号对其他信号的干扰。如图 10 所示。

2.6 铜箔处理

铜箔加工要求光滑,不允许有长线或尖角。如果无法避免,则在尖角、细长的铜箔或铜箔的边缘填上几个接地过孔。

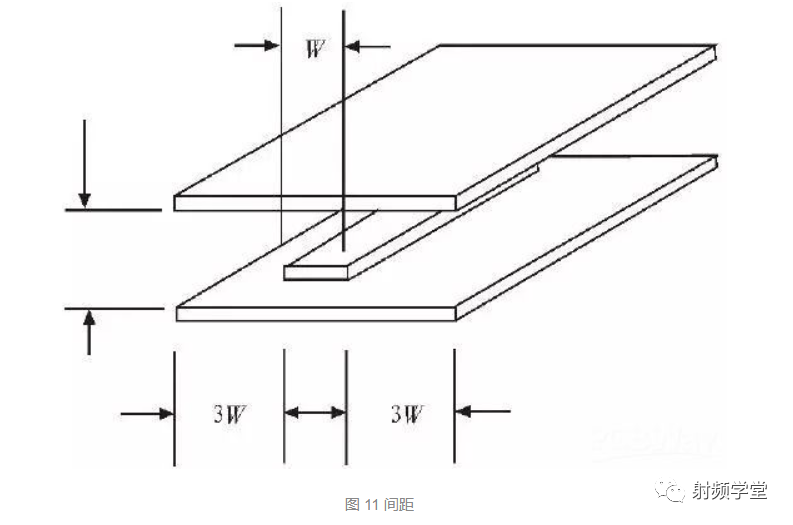

2.7 间距

射频线距离相邻接地层的边缘必须至少有 3W 宽,并且在 3W 范围内不得有非接地过孔。

同层射频线应具有共面阻抗,并应在地铜上加地过孔。孔间距应小于信号频率对应波长(λ)的1/20,并应均匀排列。

3.空洞处理

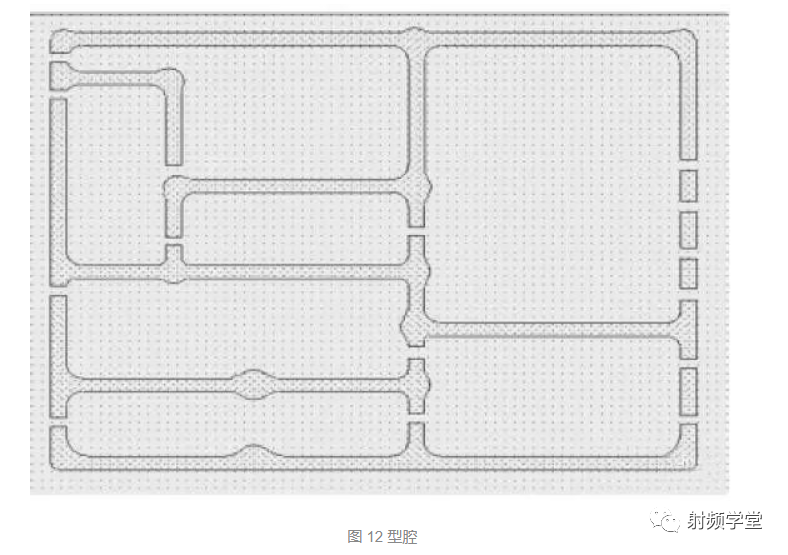

对于整个射频电路来说,不同模块的射频单元应该用空腔进行隔离,尤其是敏感电路和强辐射源之间。在大功率多级放大器中,级间的隔离也应得到保证。

整个电路的支路放好后,就是屏蔽腔的处理了。屏蔽腔的处理有以下几点:

整个屏蔽腔应尽量做成规则的形状,以利于铸造。尽量使每个屏蔽腔为矩形,避免方形屏蔽腔。

屏蔽腔的拐角为圆弧形,屏蔽金属腔一般采用铸造成型。弧形边角便于铸造时的拔模。如图 12 所示。

屏蔽腔外围是密封的,进入腔体的接口线一般为带状线或微带线

在空腔的边角处放置3mm的金属化孔以固定屏蔽壳,并在每个长空腔上均匀放置相同的金属化孔以加强支撑。

空腔通常是开窗的,以便于屏蔽壳的焊接。型腔一般厚度大于2mm,型腔内增加2排开窗孔屏。过孔是交错的。同一排过孔之间的距离为150MIL。

4。结论

在射频电路PCB的设计中,降低电路辐射,从而提高抗干扰能力非常重要。但是在实际布局布线中,一些问题的处理是相互矛盾的,如何找到一个折中点来优化整个射频电路的整体性能,是设计人员必须考虑的问题。本文总结了工作中的一些设计经验,有助于提高射频电路PCB的抗干扰能力,希望对射频电路设计的初学者有所帮助。

最前沿的电子设计资讯

最前沿的电子设计资讯