本文共计五部分4TMednc

1.前 言——为啥要了解MOS管4TMednc

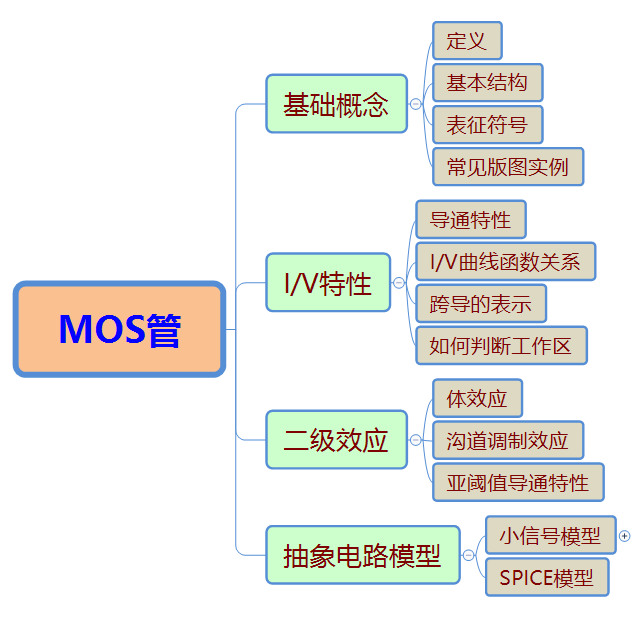

2.MOS管的基础概念4TMednc

3.MOS管的I/V特性4TMednc

4.MOS管的二级效应4TMednc

5.MOS管的抽象电路模型4TMednc

(全文阅读大概需10分钟,内容多有不严谨甚至是调侃的成分,大家看看图个乐,加深下印象。如果你在阅读本文某些地方,有那种言而不明的朦胧感的时候,那一定是博主自己也没整明白,开始在划水,所以更多专业的知识还是希望大家下来看看书复习下,当然最后还是希望本期内容对您开卷有益)4TMednc

———————————4TMednc

都说酒是穿肠药,色是刮骨刀,那么在现代电子系统中,咱门的MOS管大哥,便是传统真空管电子以及分离式固态射频电路的意大利炮,正逐步用他那无与伦比的性能、超低的功耗、极小的尺寸把传统工艺电路轰进了历史博物馆,当然也在不断地提高着大家对集成电路的认知。

为了后续设计稍微复杂的射频有源电路,本期主要介绍下MOS管的基础。我们知道在射频微波电路中Cascode和吉尔伯特单元是最为常见的电路结构(LNA、PA、Mixer、VGA、PS等电路中常常有使用到),那么在开聊这些稍微复杂的电路结构之前,咋门先看看下面的一个简化的电路,大家可先停下来,思考下:

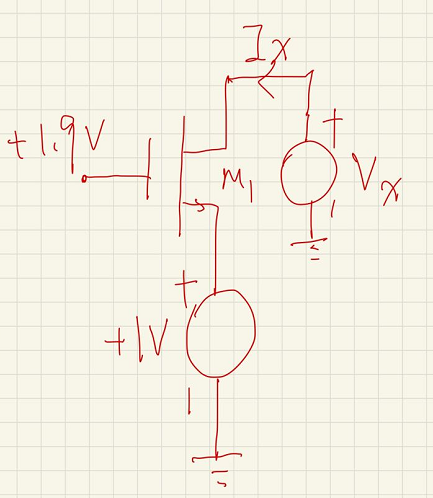

问题导入:如下图所示,假定Vth0=0.7V,忽略沟道调制效应和体效应(即lambda=0,gama=0),分析下图中电路,当Vx从0V变化到3V时,Ix是怎么样的一个响应曲线,同时M1管子是怎么样工作的???

(小提示:大家伙可以分三种情况((0,1);(1,1.2);(1.2,3))去讨论结果,如果有疑问可以加微波射频网的小编好友然后入群讨论,文末有小编的微信二维码)

好了,言归正传,本篇博文的主要目的是:希望通过总结概括MOS管的基础知识,1:给在校学生一个学习提纲;2:给正在求职面试的同学一个方便查阅的途径;3:也希望本期内容可以给从业人员一个温故而知新的小文库。因此,下面将按照如下内容进行展开:

MOS管,是MOSFET的简写(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET),MOSFET即为金属-氧化物半导体场效应晶体管,当然我们平时还是叫MOS管比较自然一点,当然我们在实际工程中为了把NMOS和PMOS做在一起,用的比较多的还是CMOS(互补型金属氧化物半导体)。

看完上面的一段话,大家伙儿是不是还是一脸蒙圈,抛砖老哥你在说什么???你写的汉字我都认识,但为何我的大脑,任然不知道你在讲啥啊!!!

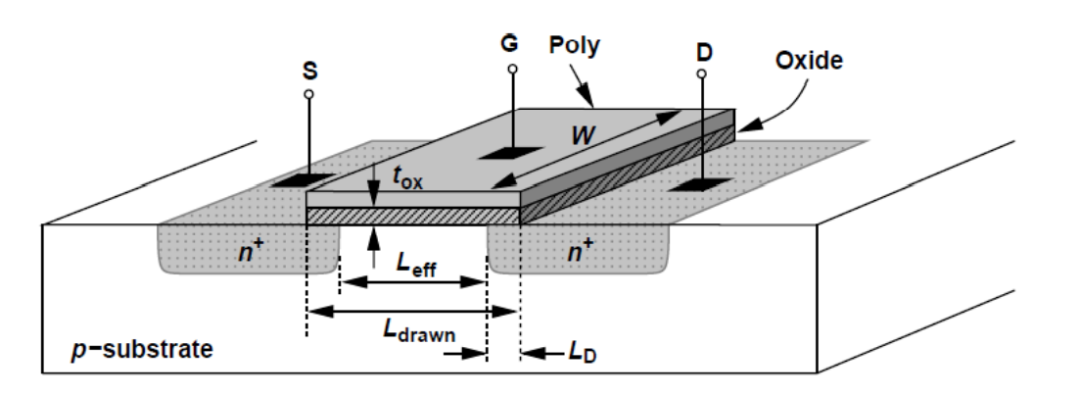

MOS管分为NMOS和PMOS,我们先抛开各种复杂的工艺流程不说,先看看NMOS它的庐山真面目,如下所示:

首先搞明白我们为什么要做MOS,其实简单地说就是我们需要有一个器件可以以小博大,四两拨千斤,通过较小的电压去实现对大的电压摆幅的输出(也就是放大作用,当然也可以是控制有无输出,即也可以做开关)。

好了,既然MOS管是用来做控制(以小博大)器件的,那么必然有这样一个三角关系:A和B作为发起方和受用方,而C呢就作为调控方,就好像上面的一根小小的管子,把两杯水给安得明明白白。

在实际的工艺中,咱们就见到了如上图提到的NMOS结构,其中D和S就是发起方和受用方,我们通常把D叫做漏极,把S叫做源极(当然只是这么叫,在某些特定的电压下,他哥俩的身份是可以互换的),然后G我们把它叫做栅极(就是中间人,你也可以把它叫做以小博大的皮条客),皮条客G栅极为了避免有一天东窗事发,干活的时候会用一层薄薄的绝缘氧化物薄膜把自己和D、S隔离开来,也就是上面的氧化物有一层tox的厚度。那么D和S的距离,也就是等效栅长,我们叫做MOS管的等效沟道长度Leff,(话说,台积电准备在2025年把控制D和S的距离在量产到2nm,而韩国三星更为恐怖,他准备在2027年把D和S的距离量产到1.4nm了,什么,国内呢?这个嘛,不清楚,大家伙可以留言讨论)

对了,MOS管的中文全称叫啥来着?哦,金属-氧化物半导体场效应晶体管,那么这里我们就把金属D、S、G以及氧化物薄膜为基础的场效应管结构介绍完了,然后所谓半导体嘛,自然就是说咱们的这些个栅极G、漏极D、源极S以及氧化物薄膜的办公室,当然他们的办公室不是随随便便选个场地就玩完,他们是选中了以低掺杂浓度的P衬底为场地,为了不坏事,场地和所谓的G、D、S尽量不要发生办公室恋情,至少不要影响到G、D、S干活,因此在NMOS中的P衬底所谓的低掺杂就是说正常情况下基本不导电,只是提供场地的作用(当然,都说日久生情,我们的衬底有时候也会对MOS管产生一些情愫和影响,我们在后面的MOS管的二级效应中,会继续来聊聊这段孽缘)。

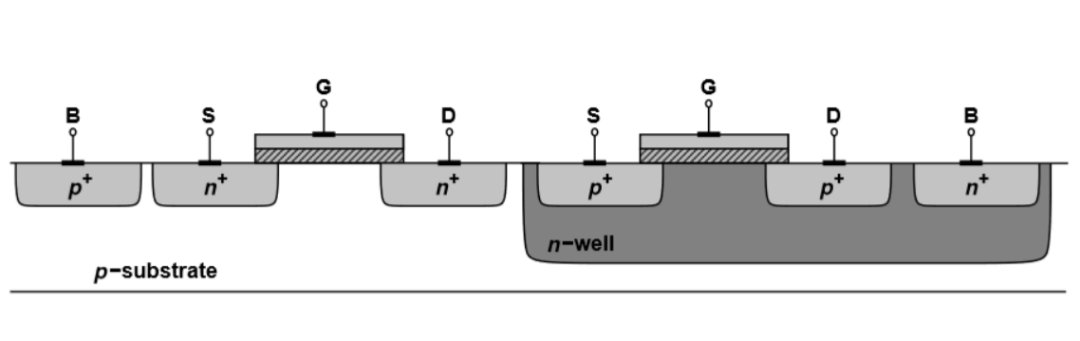

好了,上面我们大概了解了MOS管的作用的基本构成,在实际使用中,一般我们会用互补型的金氧半场效晶体管工艺,也就是大名鼎鼎的CMOS工艺,其结构如下图所示:

大家肯定会说,城市套路深,我要回农村,咱家又不是没地,干嘛委屈自己挤在一起干活?

我想说的是,小伙子光家里有地还不行啊,毕竟现在是公元2022年,现代社会讲求的是高效与合作共赢嘛!那么当我们把NMOS和PMOS放在一起的时候,往往可以达到事半功倍的效果,不过话又说回来,他俩经营的事业还是有点不一样的,NMOS和PMOS形成沟道的先决条件都是需要势垒电压的变化,因此天然而言,其存底掺杂的类型就有点区别,就好像虽然在商场里面大家都是做生意的,但是还是需要做一些隔间来区分各自的功能性,那么在CMOS工艺中,就是在P衬底上面做一个N-Well,然后PMOS就可以做到这个N-WELL里面了,这样PMOS和NMOS就可以愉快地在一起玩耍了。

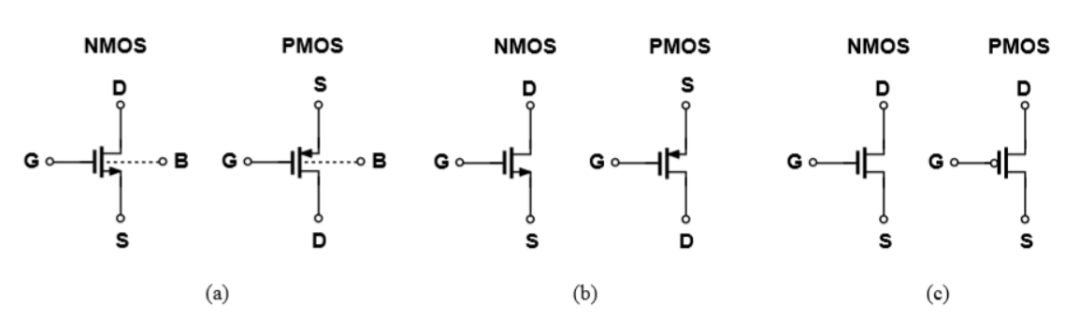

为了在交流过程中更加顺畅,我们的物理学家和工程师们就对NMOS和PMOS的表示符号进行了一些定义,这个就好像我们中国的传统象形文字一样,见下图所示:

在(a)、(b)、(c)中均是NMOS和PMOS的象形符号,大家可以按照自己的喜好去用,一般来说我们会把衬底的端电压(B,Bulk)接到地或者VDD上面,因此用(b)、(c)的时候要多一些,其中(c)的符号表达式在数字电路中用的比较多(表示开关)。

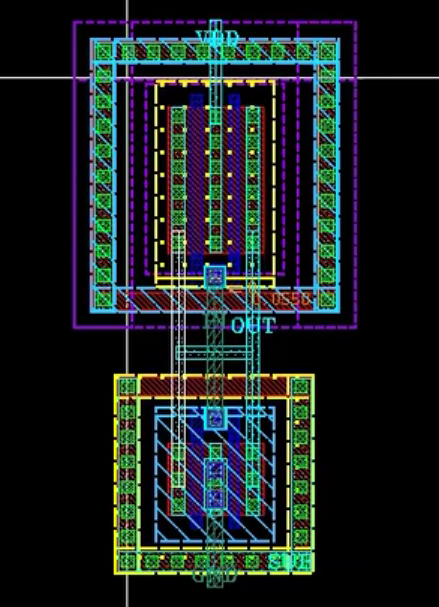

相信大家在面试的时候,很多面试官为了考查大家对NMOS和PMOS管子的结构是否理解的清楚,经常会叫大家绘制出最为典型的反相器的截面图,因此大家对上面给出的NMOS与PMOS的截面图还是要多多理解下。这里给出一个经典的反相器的原理图和版图(并非截面图),供大家参考。

好了,聊完基本的MOS管概念,下面我们进入一点数学的环节(不要被吓着,其实这些数学公式也就是物理现象的一种表示方式,就和我们上面提到的象形文符号一样的,他使我们的表达更加精炼,因此在这篇博文中我们不做数学推导,只做大自然的搬运工),那么下面就来讨论下,到底这个MOS管咋个工作的!!!

如前面所说,我们研究I/V特性不是为了推导而推导,只是为了让我们更加清楚地了解MOS管的工作状态,在后续的表达中可以更加简洁精炼,因此我们本部分重点讨论MOS管的工作状态(主要讨论NMOS管,PMOS其实很多时候就是多一个负号,大家可以自行分析下),以及如何判断工作状态,附带地根据数学公式绘制出各个状态下的I/V特性。

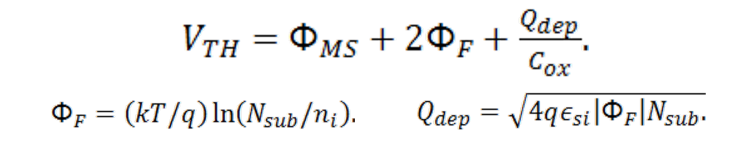

如上图所示,当我们不断升高VG,会有什么事情发生呢???我们可以看到栅极和衬底之间会等效成一个电容板,那么VG电压升高,堆积在栅极金属板的电荷就开始变多了,当电荷多到形成了一个沟道,这个时候D和S就会被导通,此时我们的VG就是所谓的“阈值电压”,VTH电压。我们接着继续提高VG,此时沟道里面的电荷密度继续增加,导致漏源电流进一步增加。好了,那么我们刚刚提到的VTH是一个定性分析出来的量,下面我直接给出半导体物理里面VTH的计算公式:

其中 是多晶硅栅和衬底的功函数之差的电压值,

是多晶硅栅和衬底的功函数之差的电压值, 里面的Nsub是衬底的掺杂浓度,q是电子电荷,ni是硅的本征载流子浓度,Qdep是耗尽区的电荷,Cox是单位面积的栅氧化层电容。

里面的Nsub是衬底的掺杂浓度,q是电子电荷,ni是硅的本征载流子浓度,Qdep是耗尽区的电荷,Cox是单位面积的栅氧化层电容。

当然我们实际计算不可能用上面的数学公式,因为这些个参数,我等凡人怕是不好测试到哦,当然就算是烧炉子的老师傅怕也是不好得到上面的参数进而求解到VTH,那么我们怎么来得到VTH 呢?下面且听我把IV特性函数细细道来,当然现在的工艺大厂们一般SPICE参数里面会有一个VTH0,我们可以直接用。4TMednc

是多晶硅栅和衬底的功函数之差的电压值,

是多晶硅栅和衬底的功函数之差的电压值, 里面的Nsub是衬底的掺杂浓度,q是电子电荷,ni是硅的本征载流子浓度,Qdep是耗尽区的电荷,Cox是单位面积的栅氧化层电容。

里面的Nsub是衬底的掺杂浓度,q是电子电荷,ni是硅的本征载流子浓度,Qdep是耗尽区的电荷,Cox是单位面积的栅氧化层电容。 最前沿的电子设计资讯

最前沿的电子设计资讯