|

简称 |

全称 |

注释 |

|

ESL |

Electronic System Level |

|

|

VP |

Virtual Prototyping/Platform |

虚拟原型/平台 |

|

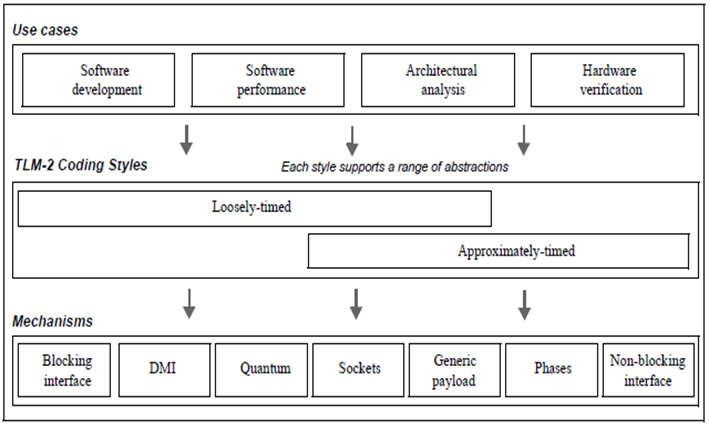

AT |

Approximately-timed model |

时序近似模型,用于性能模型 |

|

LT |

Loosely-timed model |

无时序模型,用于功能模型 |

|

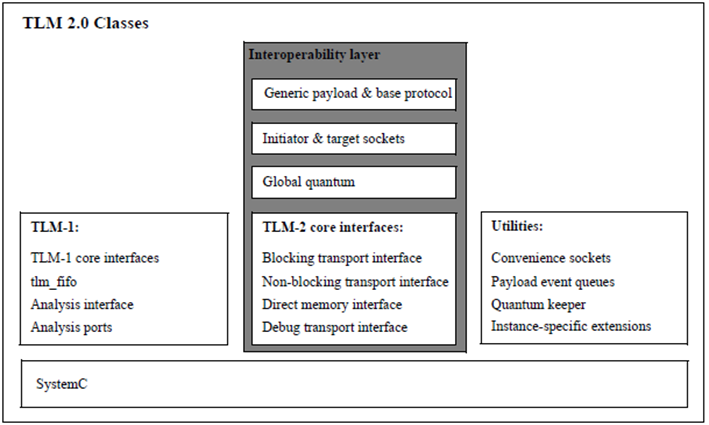

TLM |

Transaction Level Modeling |

TLM2.0 |

|

VDK |

Virtualizer Development Kits |

Synopsys |

|

CA |

Cycle Accuracy |

周期精度 |

|

PV |

Programmer View model |

|

|

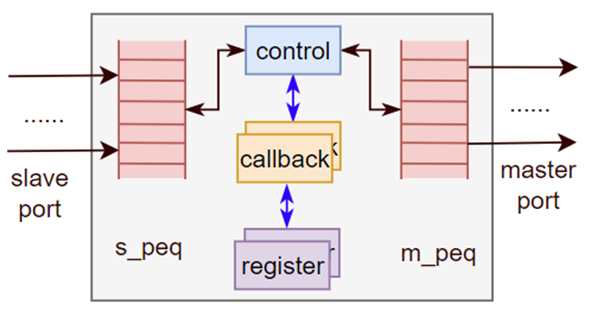

PEQ |

Payload Event Queue |

SystemC+TLM2.0 |

|

FM |

FastModel |

arm |

|

LISA |

Language for Instruction Set Architectures |

指令集架构编程语言 |

|

OSCI |

Open SystemC Initiative |

开源组织 |

|

PRD |

Product Requirement Document |

|

|

NoC |

Network on Chip |

|

|

RTL |

Register Transfer Level |

|

|

AI |

Artificial Intelligence |

|

|

GPU |

Graphic Processing Unit |

|

|

NPU |

Neural-network Processing Unit |

|

|

HLS |

High-Level Synthesis |

|

|

SoC |

System on Chip |

|

|

PCB |

Printed Circuit Board |

|

|

DDR |

Double Data Rate |

|

|

DMI |

Direct Memory Interface |

|

|

AMBA |

Advanced Microcontroller Bus Architecture |

Arm 总线协议 |

|

AXI |

Advanced eXtensible Interface |

Arm AMBA |

|

CHI |

Coherent Hub Interface |

Arm AMBA |

三. ESL发展简介

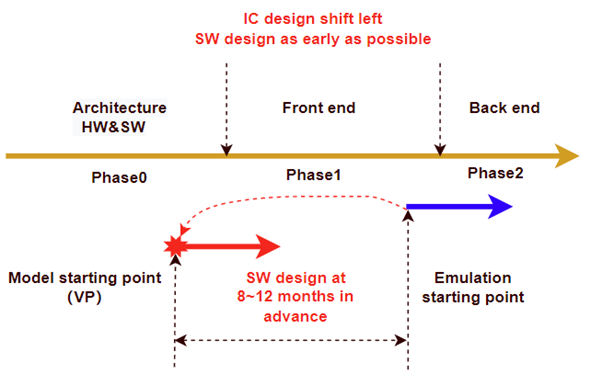

性能/架构模型(CA/AT):架构探索,评估与优化,架构设计阶段

功能模型(TL):软件提前开发,软硬件并行开发,缩短研发周期

功耗模型:功耗评估

系统设计(System Level Design):软硬件协同设计、验证与划分

Co-simulation(Model+RTL)混合仿真:包括功能和性能仿真

高阶综合(HLS):使用工具将C++/SystemC+TLM2.0模型直接综合成RTL代码

开源

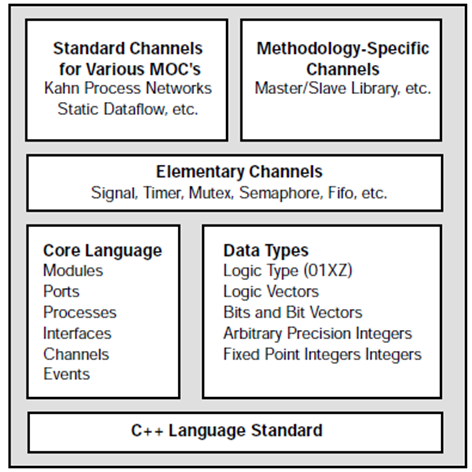

· SystemC+TLM2.0

· QEMU

· GEM5

· ……

商用

· FastModel, arm

· VDK, Synopsys

· Simics, Wind River/Intel

· ……

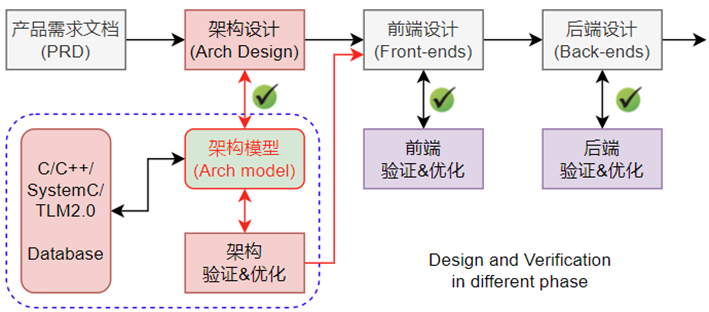

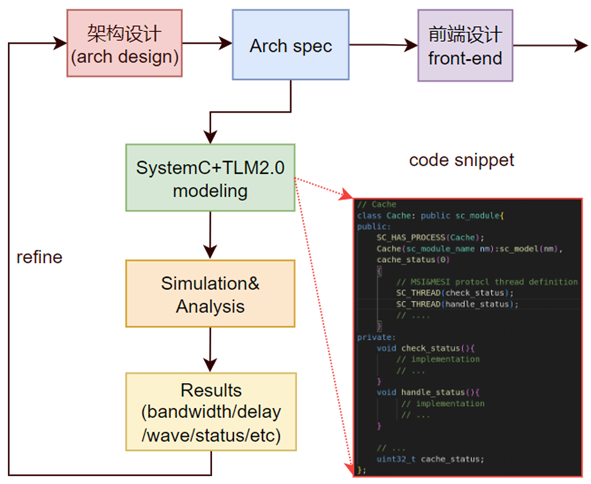

五. 性能模型

图4是简化版本的芯片设计流程,忽略其它步骤和细节,对于前端和后端而言,EDA公司可以提供明确的测试与验证平台(工具),包括方法和流程。但是对于架构设计来说,如何验证,使用什么工具或平台呢?假如芯片架构师收到了来自市场或客户的产品需求文档(Product Requirement Document, PRD),需要根据产品需求文档量化芯片的参数和指标,即定义芯片规格,确定芯片里面某些子模块的具体参数和行为,比如L1/L2/L3 cache size,总线带宽,关键模块之间的时延,内存架构等,芯片研发初期,此时RTL还未开始开发,更是没有任何平台配合应用场景来验证参数的正确性和合理性,因此如何验证架构设计成为芯片挑战之一。

模型精确性,抽象层次,可定量或定性分析

模型迭代,参数可配置,可快速迭代,可探索全新的架构(下一代)

[1]. IEEE Standard for Standard SystemC Language Reference Manual, IEEE Std 1666-2011

[2]. TLM_2_0_presentation

[3]. ESL DESIGN AND VERIFICATION 2006

[4]. A SystemC Primer 2002

[5]. systemc-from-the-ground-up-2-edition 2004

[6]. System Design with SystemC 2002

[7]. Enhanced Virtual Prototyping (Featuring RISC-V Case Studies) 2021

[8]. Complete Symbolic Simulation of SystemC Models 2016

[9]. https://en.wikipedia.org/wiki/Virtual_prototyping

[10].https://www.intel.com/content/www/us/en/developer/articles/tool/simics-simulator.html

[11]. https://developer.arm.com/Tools%20and%20Software/Fast%20Models

[12]. https://www.synopsys.com/verification/virtual-prototyping.html

[13]. https://www.qemu.org/

[14]. https://www.gem5.org/

[15]. A Survey of Computer Architecture Simulation Techniques and Tools, 2019

最前沿的电子设计资讯

最前沿的电子设计资讯