端接就是人为加入电阻来改善信号由于链路阻抗突变带来的反射问题的一种方式,并且引入成本也较低,在很多场合都有运用。但是端接电阻摆放位置一直困惑大家,或许大家只知道串联电阻需要靠近发送端摆放,并联电阻需要靠近接收端摆放,但不知道怎么衡量能够接受的距离是多少。在实际单板设计中由于芯片周边空间有限,往往可能需要从BGA中引出较长的一段走线再接上端接电阻,而这段较长走线可能会影响端接效果。下面我们就分别探讨串联电阻和并联电阻到芯片端走线距离对端接效果的影响。

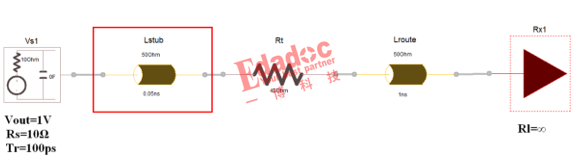

实际运用场合中串阻链路模型如图所示。串阻和驱动器之间存在一段较长的走线,这段桩线的长度会直接影响端接效果。如果串阻距离发送器较远,桩线较长,串阻就可能没有端接效果。下面我们探究一下这段桩线的长度Lstub对端接效果的影响。

下图是串阻前面桩线长度延时TD0分别为1Tr、Tr/2、Tr/5时在末端接收信号的反射振幅情况。当桩线延时达到上升时间的一半时,信号反射振幅会达到最大,桩线越短,反射振幅就越小。

上面是当信号上升时间一定,前面桩线长度变化时对串联端接效果的影响。那么当桩线长度一定时,改变信号上升时间对端接效果有没有影响呢?下面我们又来探究信号上升时间Tr分别是桩线时延TD0、3*TD0、5*TD0时末端接收信号的反射振幅情况。反射幅度随着信号上升时间的增加而逐渐减小。

根据以上结果分析可知,信号上升时间和串阻到芯片走线距离的关系会影响串联端接效果。在设计中建议桩线的延时应该不超过六分之一的信号上升时间,即TDstub≤Tr/6,这样接收端的噪声基本能够控制在10%以内。例如信号上升时间为300ps,桩线的延时应当要小于50ps,即桩线的长度不超过300mil基本不会出现问题。

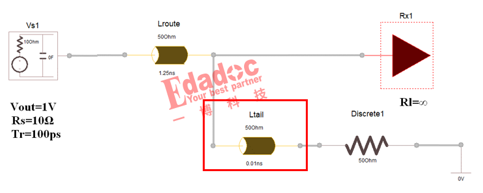

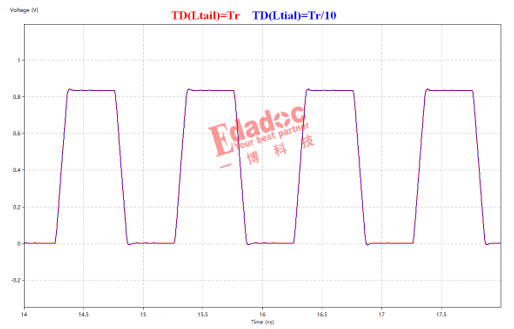

接下来我们探讨并联端接链路中电阻到末端距离对信号的影响。在理想情况下电阻最好放在接收器之后,仿真链路模型如下。传输线先连接到接收端,然后再引一段“尾巴”走线到端接电阻,端接电阻尾线阻抗与并联电阻值保持一致。这样信号先到接收端,然后再到端接电阻。这种状态下端接电阻的尾线长度Ltail对信号质量影响非常小。下面也验证了端接尾线传输延时分别是Tr和Tr/10两种情况下接收端的信号波形状态。

可以看到两个信号波形几乎完全重合,信号质量非常良好。由此分析可知,端接电阻尾线长度对端接效果几乎没有影响。

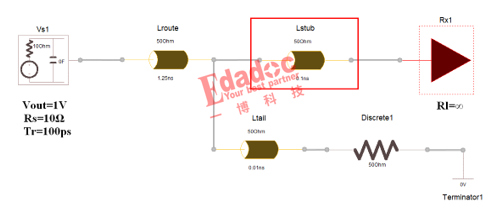

在实际项目设计中,端接不可能完全都从信号接收端接出来,总会在端接电阻分支点和接收端之间存在一段长度的走线,如下图链路模型。这段桩线的长度Lstub会影响信号接收质量,若桩线过长将削弱端接效果。

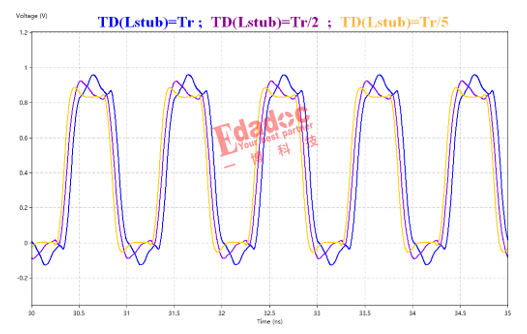

下图显示的是接收端前面桩线长度分别为Tr、Tr/2、Tr/5情况下接收端信号波形状态。可以看出当桩线长度越短,端接效果就越好。建议端接电阻前面桩线延时小于Tr/6。

当采用端接来改善信号反射时,串联阻应尽可能靠近发送端放置,建议芯片输出到串阻的走线延时小于六分之一的信号上升时间;并联电阻应尽可能靠近接收端放置,端接电阻支路尾线长度对端接效果影响较小,建议端接电阻分支点到接收端的走线延时小于六分之一的信号上升时间。这或许也是为什么到DDR5后地址线的末端端接也改成了ODT的形式。

最前沿的电子设计资讯

最前沿的电子设计资讯