1. 单通道330Gbps PAM8的微环调制器

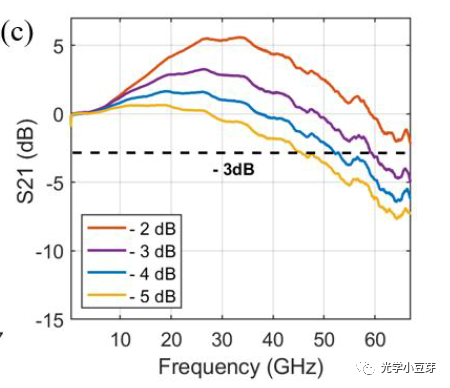

香港中文大学研究组通过调节激光器波长与微环共振波长的偏移,借助于peaking效应,实现了超过50GHz的C波段微环调制器,其带宽结果如下图所示,波长detuning量越大,peaking效应越强。

(图片来自文献1)

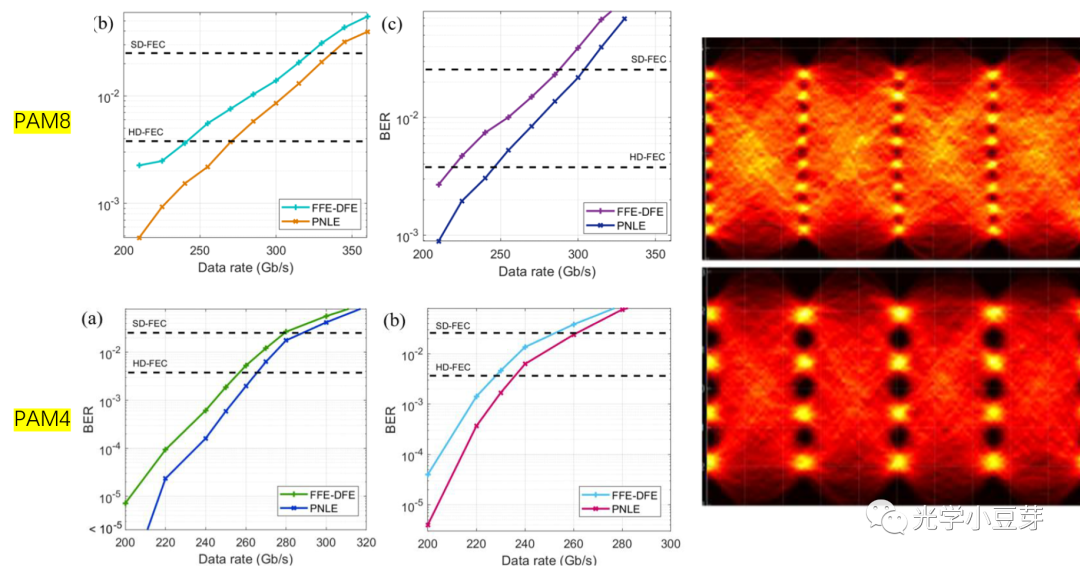

微环调制器采用lateral型PN结,半径为7.5um, Q值为5200,驱动电压小于2Vpp。研究人员分别进行了Back-to-back和引入1km光纤的链路测试,在接收端分别采用FFE-DFE(feed-forward equalizer combined with decision feedback equalizer)和PNLE(polynomial nonlinear equalizer)两种均衡方法,测试结果如下图所示,

(图片来自文献1)

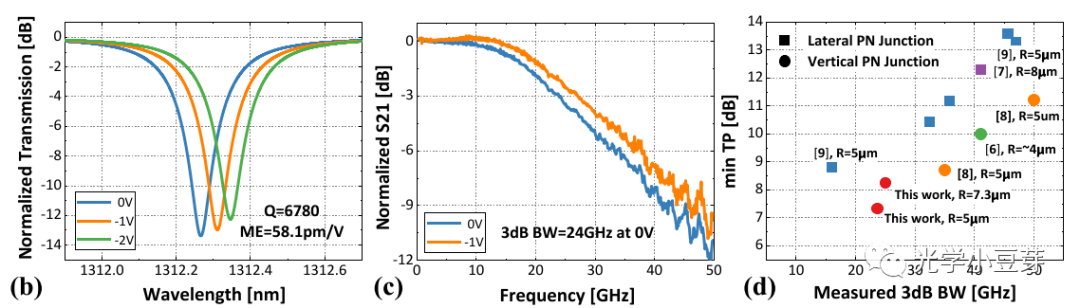

上图中20% SD-FEC的阈值为2.4e-2, 7% HD-FEC的阈值为3.8e-3, 不同情况下的最大速率如下表所示,

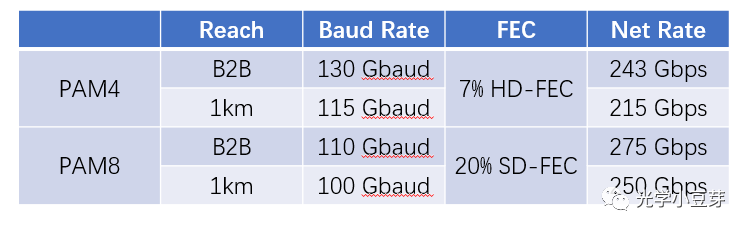

2. IMEC的低功耗微环调制器为了改善TP(transmitter penalty)和带宽间的trade-off, IMEC采用vertical型PN结构,其调制效率高于传统的lateral型PN结结构。微环调制器半径为5um, 带宽为24GHz, 驱动电压为1Vpp, TP为7.4dB,结果如下图所示,

(图片来自文献2)

(图片来自文献2)

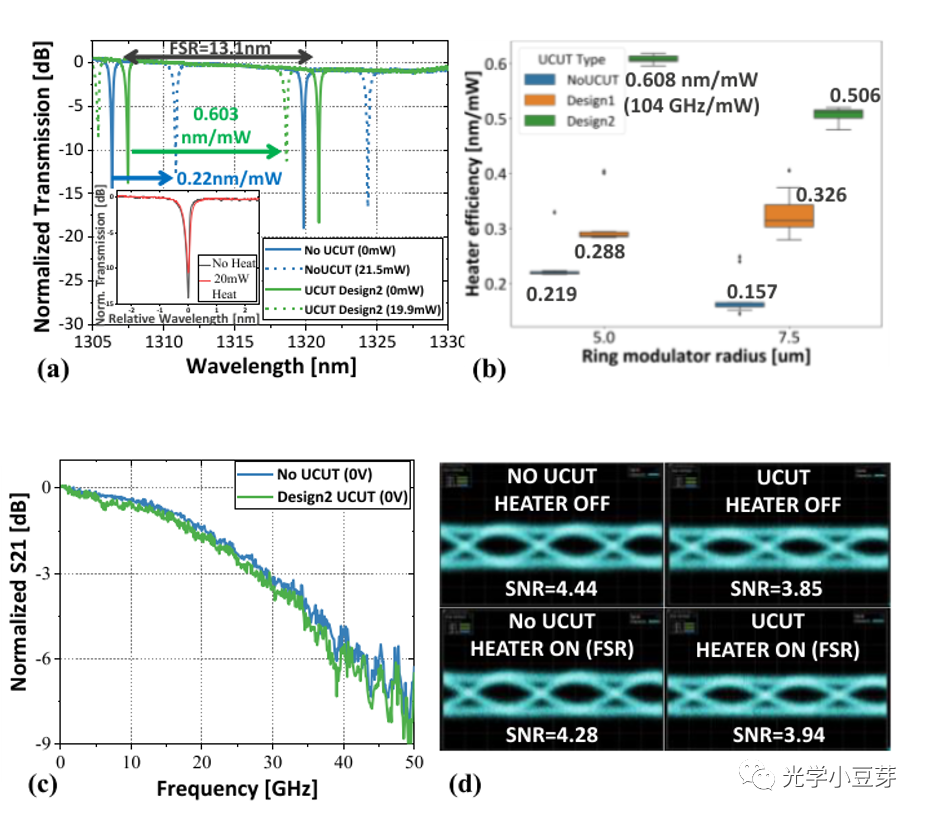

为了降低热调的功耗,IMEC采用undercut工艺,将微环区域的substrate刻蚀掉一部分,阻碍热量在硅衬底中的传导,从而提高热调效率。采用UCUT工艺后的热调效率为0.61nm/mW, 而标准工艺的微环热调效率为0.22nm/mW, 热调效率提高了2.7倍。进一步,IMEC验证了UCUT对MRM性能没有带来很大的影响,结果如下图所示,

(图片来自文献2)

IMEC将先前项目研发的14nm工艺电芯片flip-chip到硅光芯片上,bump的pitch为50um。封装之后的热调效率降低为0.32nm/mW,这主要是由于一部分热量通过bump进行传递。

IMEC分别对Tx端和Rx端进行了测试,激光器输出光功率为9dBm,Tx端可以支持40Gbps的速率,ER为5.2dB,对应的能效为0.17pJ/bit。Rx端支持44Gbps的速率,能效为0.27pJ/bit。整个link支持40Gbps的信号速率,Rx端的OMA为-8.4dBm。整个link的BER为3.2e-13。测试结果如下图所示,

(图片来自文献2)

IMEC对整个link的功耗进行了分析,微环调制器的热调功耗为0.71pJ/bit, 微环滤波器由于采用了double-ring的设计,热调功耗为0.38pJ/bit,激光器的功耗为1.9pJ/bit(假设激光器的wall-plug效率为10%),整个系统的功耗为3.5pJ/bit。链路中光栅耦合器的损耗较大,为3.65dB/facet, 三次耦合带来近11dB的损耗,该指标还可以进一步优化,进而降低功耗。

3. 采用DBI封装技术的硅光收发器

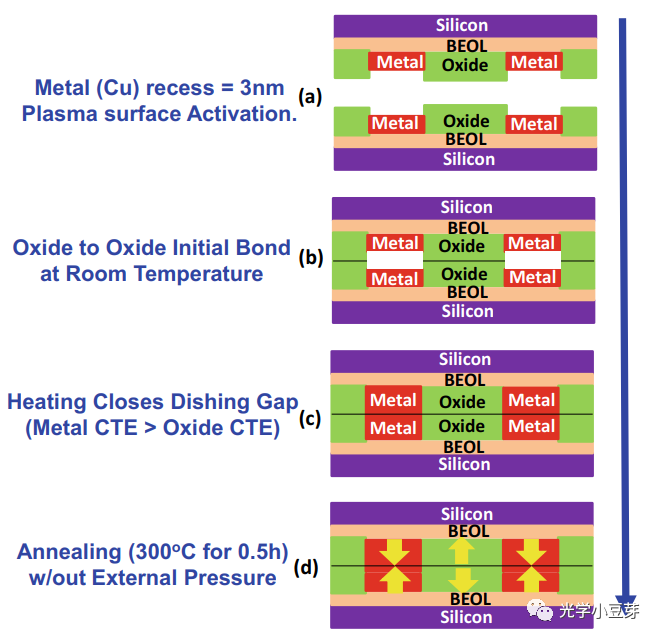

UC Davis研究组协同几个合作单位,开发了基于DBI封装技术的硅光收发器。DBI的全称是direct bonding interconnect, 也称为hybrid bonding。传统的封装技术采用solder bump实现芯片间的电互联,但是当pitch小于20um时,solder bump工艺实现起来比较困难。而DBI技术则可以实现20um以下的pitch,带来更大的互联密度。典型的工艺步骤如下图所示,在室温下两片chiplet或者wafer间通过oxide间的相互作用直接bonding在一起,接着在高温下凹陷处的金属发生膨胀,最后进行退火,通过内部的应力作用,金属间形成稳定的bonding。

(图片来自https://link.springer.com/chapter/10.1007/978-981-16-1376-0_8)

由于采用DBI封装技术,bump的寄生电容大大减小,从传统的80fF降低到5.5fF, 降低了一个数量级。寄生电容的减小,使得Rx端的噪声更小,TIA的增益也可以更大,进而使得Rx端的灵敏度要求降低。

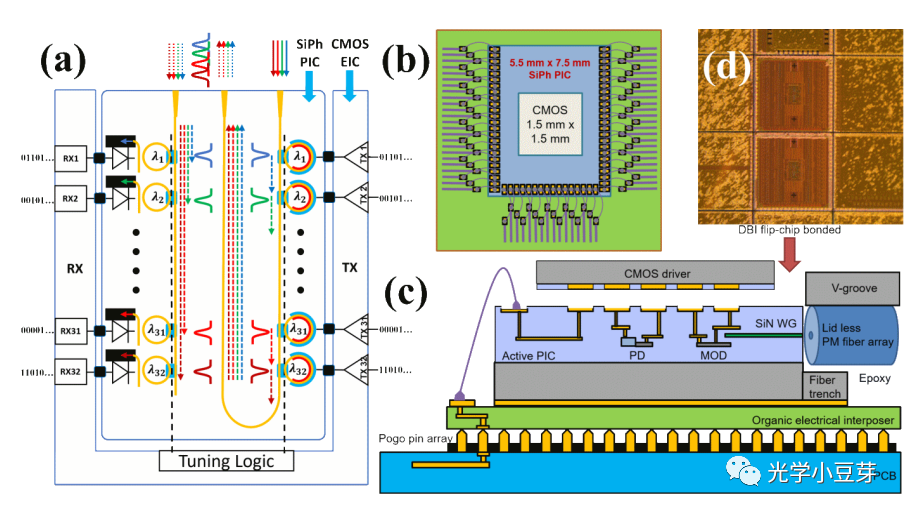

UC Davis没有透露太多的微环调制器设计细节,其采用AIM Photonics的12寸硅光工艺,光芯片的尺寸为5.5mm*7.5mm, 包含32个微环调制器和32个微环滤波器。电芯片采用GlobalFoundries的12nm FinFET工艺,芯片尺寸为1.5mm*1.5mm, 是PIC面积的5.45%。整个3D集成的芯片如下图所示,EIC通过DBI技术倒装在PIC上,bump pitch为20um。PIC与基板间通过wire-bonding互联。PIC芯片采用基于SiN的边缘耦合方案。

(图片来自文献3)

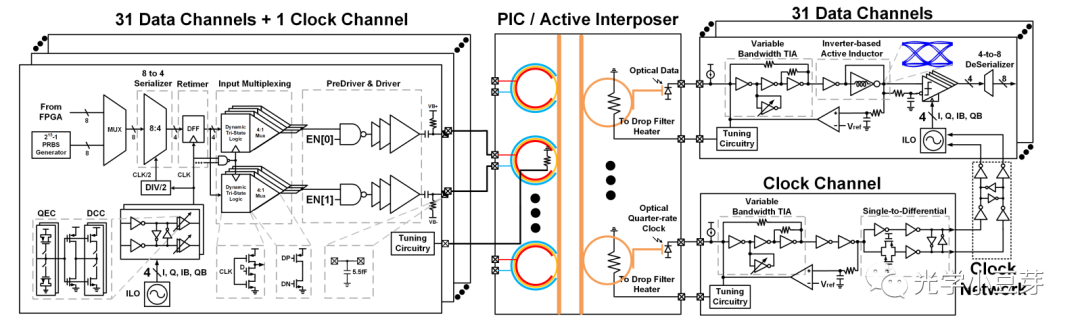

电芯片内部包含32通道的driver和TIA, 也包含serializer和deserializer,如下图所示。32路通道中,有一路是用来传递时钟信号,其它为数据通道。Tx端采用0.9V的电源,输出1.8Vpp的驱动信号。Rx端的带宽可以动态调节。

(图片来自文献3)

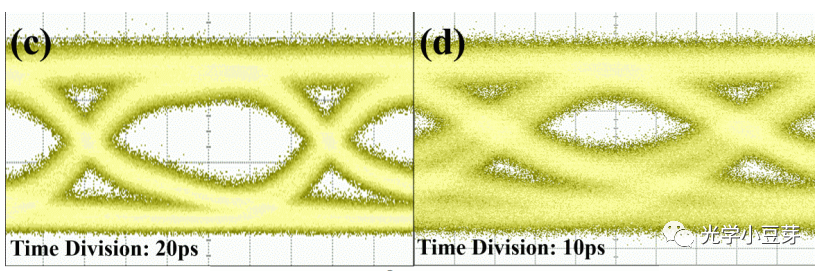

微环滤波器的热调效率为0.27nm/mW。Tx端在10Gbps和18Gbps的眼图如下图所示,

(图片来自文献3)

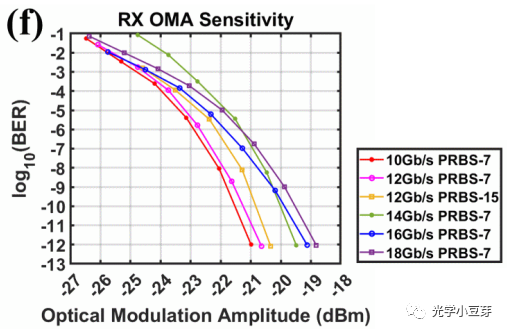

Rx端的测试结果如下图所示,12Gbps时的OMA灵敏度为-20.3dBm, 18Gbps时的OMA灵敏度为-18.8dBm。

(图片来自文献3)

整个系统的功耗为0.691pJ/bit(不包含激光器功耗在内)。功耗分解如下图所示,serDes占整个电芯片功耗的70%。

(图片来自文献3)

以上是对OFC 2023上微环调制器的最新进展,

1) 从器件层面看,可以通过光学peaking效应来实现更大的带宽,也可以使用vertical型PN结构,实现更大的调制效率,降低对驱动电压的要求。

2) 从功耗层面看,可以利用undercut结构来降低热调的功耗,也可以采用新型的DBI封装方案,减小寄生电容,降低Rx端灵敏度的要求,进而减小系统的整体功耗。

3) 从系统层面看,微环调制器的设计优化需要与电芯片深度绑定,进行联合仿真设计,尤其是对微环工作点的控制。新型的光电封装方案也值得探索。

最前沿的电子设计资讯

最前沿的电子设计资讯