作为高速信号传输的重要的指标之一,损耗,无论是对硬件工程师,设计工程师还是我们SI工程师来说,都会是非常的关注。而对于像背板传输这种长距离的走线系统或者像芯片测试板要求损耗极小的情况,传输线的损耗在总的系统损耗里面一定是占到一个大头的位置。尤其是在板材和走线长度已经定下来的情况下,传输线的线宽几乎就成为了让损耗能逆袭的唯一的一根救命稻草了。

根据我们对高速理论的理解,线宽对传输线损耗的贡献是非常正向的,在其他条件不变的情况下,传输线的线宽越宽,传输线的损耗会越小,而且会一直是这个趋势不变。那么,粉丝们会不会很容易就产生了两个想法,一是,只要我在PCB设计中能把传输线走得更宽,而且能控制到阻抗的情况下,我们就能够在其他条件不变的情况下把损耗做得更小;另外一个想法就更大胆了,是不是如果我的线宽能做到无限大之后,传输线的损耗理论上就能够接近零损耗呢?

高速先生的确很喜欢有想法的粉丝,这样可以激发出更多的灵感。喜欢归喜欢,高速先生还是要用数据来说话。这样吧,高速先生就做一块测试板来验证下这个问题,毕竟实践才是检验真理的唯一标准嘛!

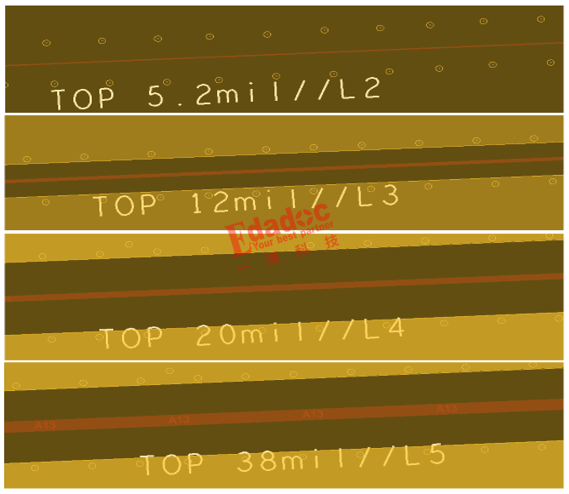

测试板的设计也很简单,我们叠层和板材是固定的,我们要验证的走线是在TOP层,那么要增加线宽而且又能控制到阻抗(单端50欧姆)的话,我们需要做的就是去挖空若干层走线的参考层,也就是让参考层更远,这样传输线的线宽才能够不断的增大。下面是我们精心设计过的叠层,展示前5层如下所示:

为什么只展示前5层呢,因为我们验证的走线是从TOP层参考L2层的地平面一直到参考L5层的地平面,这样的话,随着参考平面的变远,TOP层的传输线线宽在同样控制50欧姆的情况下才能不断变大,实现我们要研究线宽和损耗关系的目的。

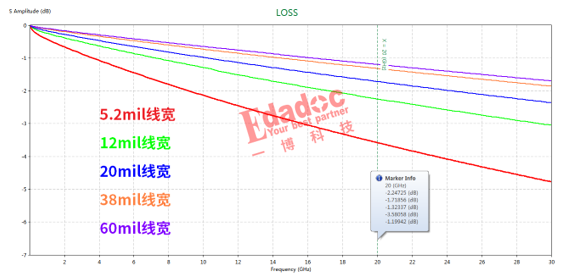

那么参考到不同层之后,线宽的变化范围大概是多少呢?经过计算,我们参考不同层的线宽变化就非常非常明显了,从参考L2层的5.2mil变到参考L5层的38mil!

基本上38mil已经是我们走线线宽的天花板了吧,那么我们分别来看看从细线宽到宽线宽的情况下,损耗到底能改善多少的量级呢?

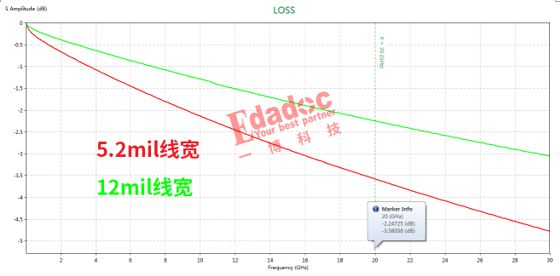

首先我们验证从5.2mil到12mil的变化,结果如下所示,标注了一个20GHz比较高频的点,损耗从大概3.58db改善到了2.25db,损耗改善了40%左右。

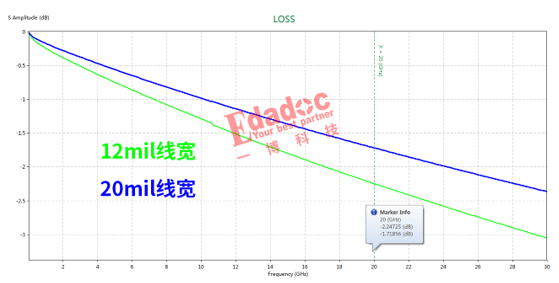

恩,看起来非常的不错,改善量也很大,让我们不得不憧憬线宽进一步增加后的效果了。好,那么我们接下来去对比12mil线宽增加到20mil的情况下,损耗的改善量。从下图结果来看,从2.25db改善到了1.72db,损耗改善不到25%了。

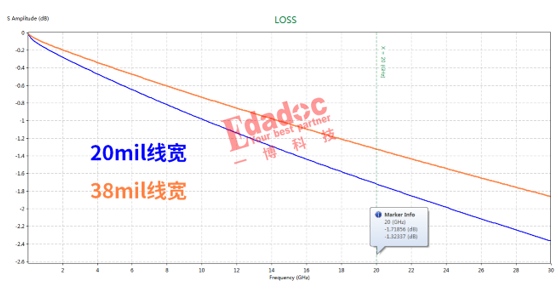

呃,也还行吧,至少也算是个比较大的改善量了,那我们继续看从20mil增加到38mil线宽后的结果。真没想到,在20mil往上差不多加一倍的线宽情况下,只是从1.72db改善到了1.32db,也就是20%多点的改善量,远远比我们想象的改善量要小!

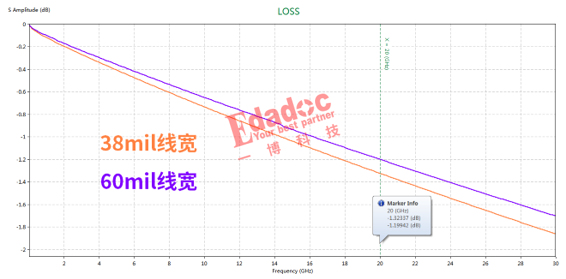

行吧,为了让大家死心,高速先生再参考多几层,做一个更宽更宽的走线的case,我们做出了一个60mil的线宽,那我们来对比下60mil线宽和38mil线宽的改善量。损耗大概从1.32db减少到1.2db,改善量只有不到10%了。

最后我们再把上面的几种case摆在一起,让大家更为直观的看到线宽不断增加情况下,损耗改善的量级。

最后再回答下上面提到的两个想法,一是随着线宽的增加,损耗的确是会不断的减小,趋势是没错的。但是另外一个想法可能就只能真的是想想了,线宽增加到一定的宽度后,损耗改善的量级会越来越小了,绝对不会得到一个很接近零损耗的结果了。至于是为什么呢?这个就当本期的问题留给大家来思考了哈!

最前沿的电子设计资讯

最前沿的电子设计资讯