关于DDR的案例,高速先生已经分享过很多期的文章了,有通过修改主控芯片的驱动解决问题的,有通过修改PCB走线的拓扑来解决问题的,也有通过调节端接电阻来解决问题的,相对于下面即将登场的解决方法而言,上述的方式都突然显得很复杂了。不信?那我们一起往下看呗!

又是一个睡眼朦胧的下午,雷豹最近刚结束掉手上的所有项目,在公司美美的睡上一个午觉醒来后,正值百无聊赖之际,师傅Chris为了防止雷豹继续“颓废”,刚好手上接到了一个DDR的debug项目,因此毅然决然的分配给了雷豹,这突如其来的“锅”让雷豹瞬间惊醒。

这个DDR有问题的板子是我们设计的,但是并没有进入到仿真部门去做仿真,客户的描述也非常的直击问题点,就是……DDR4跑不到额定的2400M的速率!

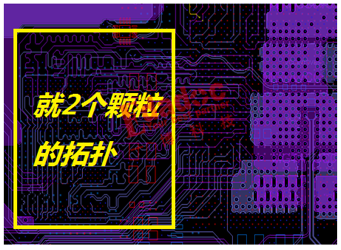

只想板子跑到额定2400M的速率,客户这个要求一点也不过分,但是我们的设计工程师看了看之前的板子,也找不到太多的优化方案。因为本来就只有1拖2的2个DDR颗粒的拓扑,正常来说都比较好做,工程师在走线上也参考了之前内部培训的设计方法,照道理不应该出问题啊!

雷豹是个直直的仿真爱好者,这时候他也先不管怎么去优化,也没去找原因,就先拿到主控和颗粒的模型先按照这个版本做了个通道的仿真,不得不说雷豹的仿真技术是真的牛叉,很快就仿真出了也是fail的,能够和测试情况相对应。

他很自豪的和师傅Chris汇报,只见Chris淡淡的一笑,反问到雷豹,那是哪里出了问题呢,又应该这么去从PCB设计上去优化呢?雷豹虽然在和Chris汇报仿真结果之前其实也有想过师傅会这样问,奈何雷豹也打开PCB文件去看了,重点关注了走线的拓扑结构,对比和我司设计部之前做过的类似设计的方案,两者在走线上是长度,拓扑结构上都是非常接近的。一句话,也就是找不到问题点呗……

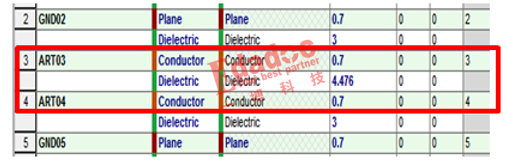

Chris看雷豹好像没辙了,那就只能给雷豹一点暗示了。只见Chris不慌不忙的打开PCB文件,雷豹见Chris直接跳过了检查PCB上的走线这一步,径直的打开了叠层设置,然后给雷豹指一下这个地方,没错,指的就是下面这个红框框的地方。

雷豹感觉好像懂了一点了,原来该客户为了比demo板有更好的成本优势,在设计上使用了相邻层走线的这个方法,也就是我们所说的GSSG的叠层结构,这样的话的确在层数上可以省下几层,但是就会带来其他方面的一些坏处。雷豹一直都是在关注走线是怎么怎么走的,和demo板是如何如何相似,却没注意到叠层设计本身已经有这么大的差别了。

这时既然客户要省成本嘛,高速先生肯定还是尊重客户的这个意愿的,就在客户这个省成本的设计中去想办法改善信号质量,从而达到要求。鉴于雷豹已经隐约知道了问题的原因了,Chris也不立马点破,还是希望让雷豹自己能独立解决。之前已经说了,要保持这个省成本的层数不变,在这个前提的下去解决问题。

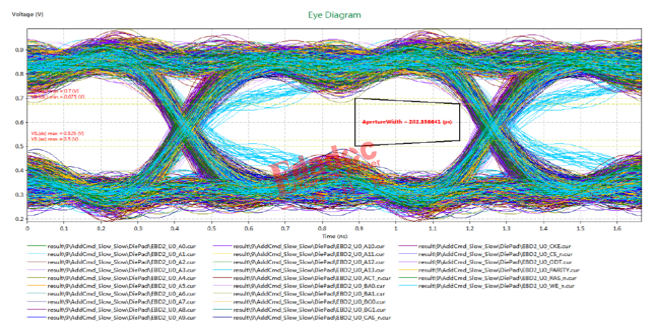

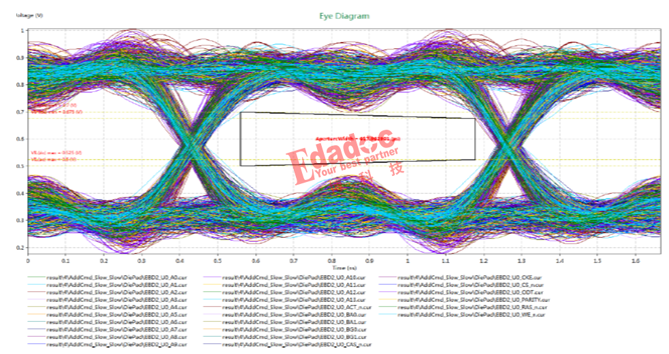

雷豹左想右想了半天,突然灵机一动,只见他对了叠层设置一顿调节,又相应的通过改变线宽来保证原有的走线阻抗不变。之前是12层板,现在也还是12层板,总体的板厚也没发生变化。然后雷豹带着他自己优化后的仿真结果再和Chris汇报,这次雷豹带来的仿真结果果然有了明显的优化,从仿真验证上,已经能把信号质量变成PASS了!

Chris看看雷豹优化后的PCB文件,发现走线的拓扑长度都没有变化,只是从叠层上做了下文章,这也和Chris预想的方案是一样的,然后就给雷豹点了一个大大的赞,雷豹寻思这一路debug过来,虽然最后想到的方案不难,但是发现和解决debug问题的过程却是艰辛的,不过总算自己解决掉了,也积累了一个新的技术点!

最前沿的电子设计资讯

最前沿的电子设计资讯