内存的稳定性,离不开RAS功能。提起RAS,熟悉DDR的小伙伴们一定记得行地址选通信号(Row Address Strobe, RAS),不过这个信号跟本文没啥关系,为了避免大家概念混淆,先说明一哈。

言归正传,今天要介绍的是另外一个RAS(Reliability,Availability and Serviceability),即可靠性、可用性和可维护性的简称。RAS功能一方面可以通过调整信号规避风险,另一方面,在发生错误时及时发现并进行修正,以延长系统正常运行的时间,通俗点说,就是没事不找事,有事不怕事,当然了,这么通透的功能不是某一项技术就能搞掂的,RAS功能通常是一组技术的合称,DDR5能稳住,RAS功能功不可没。闲言少叙,一起上车吧。

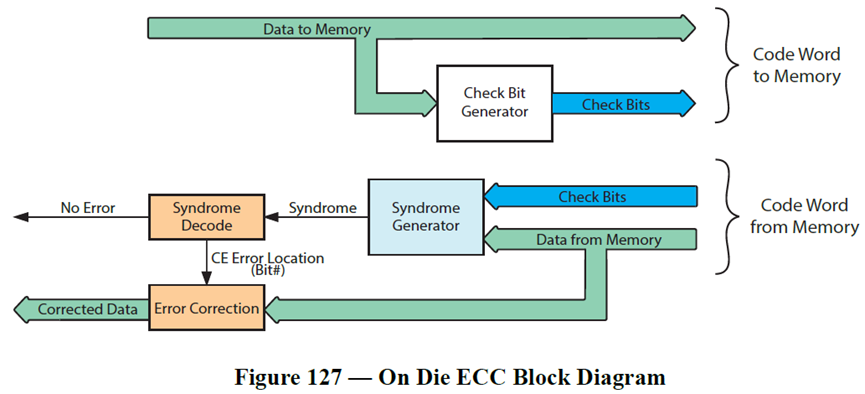

【提升1】片上ECC (On-Die Error Correction Code)

随着DDR5信号速率的增加和芯片生产工艺难度的加大,DRAM内存出现单位错误的风险也随之增加,为进一步改善内存信道,纠正DRAM芯片中可能出现的位错误,DDR5引入了片上ECC技术,将ECC集成到DDR5芯片内部,提高可靠性并降低风险,同时还能降低缺陷率。

看到这里,高速先生似乎已经能猜到大家最关心的问题了:片上ECC的使用是否意味着可以不用单独的ECC颗粒了?很遗憾,答案是否定的,因为On-Die ECC无法纠正芯片外或者模块与内存控制器之间的DDR通道中的错误,因此,之前常用的边带(Side-band)ECC颗粒在必要的情况下还是要保留的。

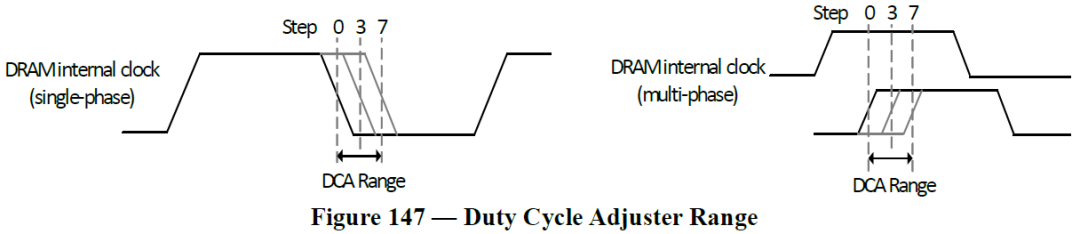

【提升2】占空比调节器 (DCA,Duty Cycle Adjuster)

占空比调节器(DCA)支持主控通过调节DDR5内部占空比,在一定的范围内补偿数据选通信号(DQS)和数据信号(DQ)的占空比失真,该功能通过调整DQ和DQS信号的占空比,巩固了读取数据的稳定性。

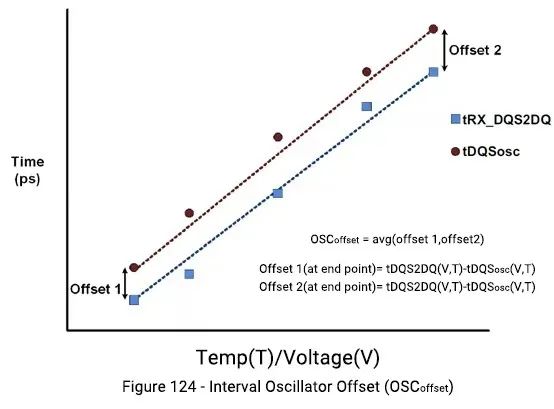

【提升3】DQS内部延迟监控(DQS Interval Oscillator)

随着DDR DIE上的电压和温度变化,DQS时钟树延迟将发生偏移,可能需要重新训练(re-train)。DDR5包括一个内部DQS时钟树振荡器,用于测量由主控确定的给定时间间隔内的延迟量。DQS振荡器为主控提供是否需要重新训练,以及潜在误差大小等重要信息。主控可以使用此功能定期重新训练通道,以补偿DRAM中电压和温度变化引起的延迟。

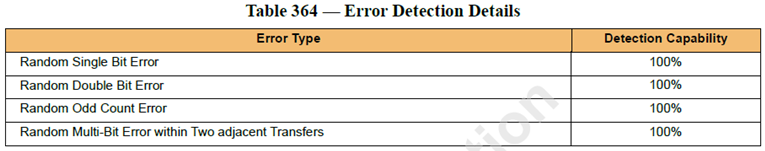

【提升4】数据读写的循环冗余校验 (CRC, Cyclic Redundancy Check)

循环冗余校验是数据通信领域中一种常见的查错校验技术。其基本原理是:将固定数量的校验位附加在需要传输的数据后面,发送端对校验位进行特定的运算并发送,接收端在接收数据后对校验位进行运算以检查是否出错。CRC保证了数据传输的正确性。

DDR4仅支持数据写操作的CRC,DDR5则将CRC功能扩展到数据的读操作,进一步保证了数据传输的可靠性。

【提升5】数据的反馈判决均衡 (DFE)

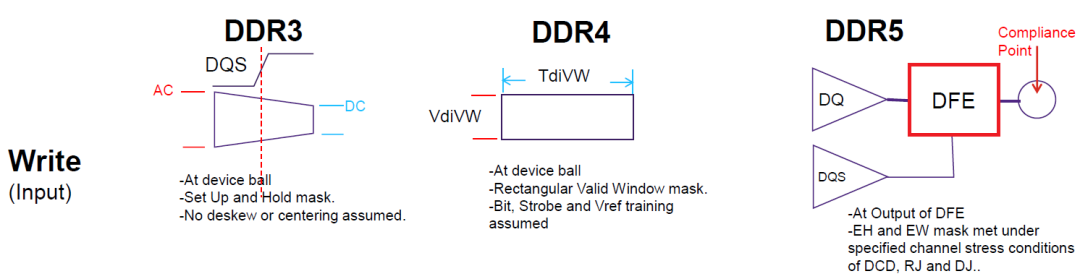

对于数据信号,随着速率的进一步提升,DDR5采用了之前在高速串行信号中才会使用的反馈判决均衡技术(DFE),以减少信号衰减和码间干扰(ISI)的负面影响,增加了信号眼图的优化手段,为数据信号的高速传输提供了保障。

关于DDR5数据信号的DFE功能,高速先生之前有专门写过一篇文章进行介绍,这里就不再赘述。

篇幅所限,本文对DDR5的RAS功能简介就到这里,正是由于多种RAS新功能的加持,才一定程度上保证了DDR5提速后的稳定性。

最前沿的电子设计资讯

最前沿的电子设计资讯