作者:王锐

"时序"话题继续殴,说好的围殴一个话题,要殴就殴他个精神抖擞,殴他个四脚朝天,殴到大家爽为止……

相信大家还有印象,在文章《PCB设计的十大误区 - 绕不完的等长4》末尾,提出的问题是:有哪些因素会导致实现了等长设计,却没有等时?高速先生把大家的观点综合之后给出了评论,其中影响较大的因素有同组不同层、过密的蛇形绕线、跨分割、玻纤效应、封装长度等。

对很多有刨根问底精神的网友来说,读到这里大概就会产生这样一个疑问:高速先生,那这些因素对信号传输延时到底有多大的影响呢?求明示…

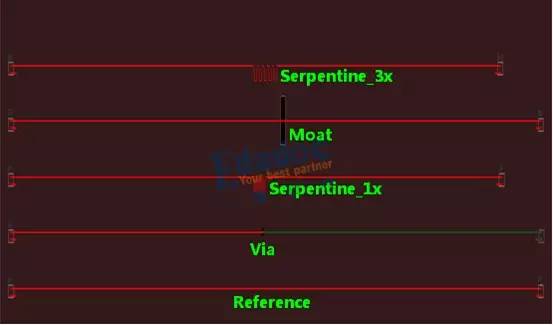

针对此问题,高速先生模拟了下列五种情况来进行对比,五种情况分别是:

1.Reference(6inch 50ohm的微带线)

2.Via(6inch 50ohm的微带线,中间有一个表层到底层的换层孔,过孔长1mm)

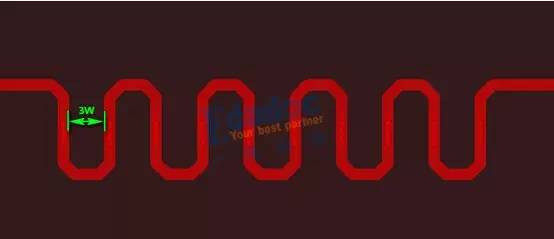

3.Serpentine_1x(6inch 50ohm的微带线,其中有500mil蛇形线,蛇形线间距为1倍线宽)

4.Moat(6inch 50ohm的微带线,微带线横跨一个50mil的分割线)

5. Serpentine_3x(6inch 50ohm的微带线,其中有500mil蛇形线,蛇形线间距为3倍线宽)

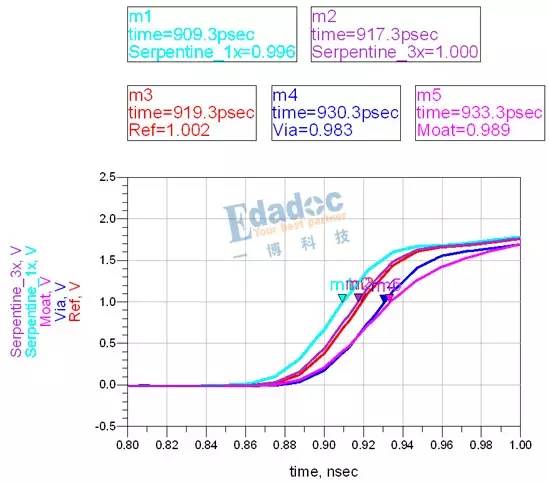

直接看仿真结果:

Via与Reference的时延差:m4-m3=11ps

Serpentine_1x与Reference的时延差:m1-m3=-10ps

Moat与Reference的时延差:m5-m3=14ps

Serpentine_3x与Reference的时延差:m2-m3=-2ps

当我们还在为5mil,10mil的长度差异而苦苦绕等长时,10ps、20ps的时延差异难道还不能引起我们的足够重视吗?!

预知后事如何 且听下回分解。下期将分享:为什么会出现此类时延差异?

最前沿的电子设计资讯

最前沿的电子设计资讯