作者:袁波

高速先生前几期的自媒体文章里多次提到了时序,并且也写了很多时序方面的文章,这些文章都从不同的角度对时序的概念进行了阐述。作者读完之后深受启发,这里,作者也把自己对时序的理解表达出来,供网友们参考。

接触到时序概念,是从学习DDR布线开始的。作者以前只知道一个差分对里面的两根线需要等长,等长的原因是保证P和N两根线上传输的信号同时到达接收端,这样就不会有共模信号的出现。然而,在DDR实际布线中,难点在于各组信号间的线长匹配。

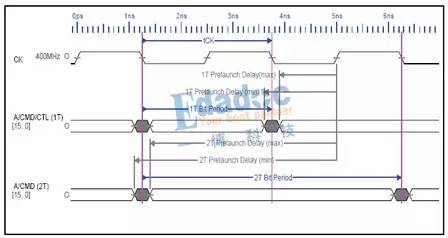

我们知道,DDR的四组信号之中,地址/命令/控制信号都是参考时钟信号的,数据信号参考DQS。具体来说,就是要这些信号波形的相对位置之间存在一定的约束。时钟与地址/命令,控制之间的波形位置对应关系如下,如下图1:

图1

从图1可以看出,理想情况下,地址/命令,控制信号的波形边沿应该和时钟信号的下降沿对齐,这样才能保证时钟信号的上升沿在地址/命令信号的中间位置,只有这样,信号传输到接收端为建立时间和保持时间留足裕量。图一中的灰色窗口就是不确定区域,也是我们在设计的时候需要考虑的,一般我们可以通过查看芯片的Datesheet来查阅Prelaunch的最小值与最大值,这个是芯片本身的参数,与布线无关。说了这么多,系统在工作的时候,时钟与地址/控制信号波形之间的位置关系到底是什么样的呢?让给我们来看看下图2

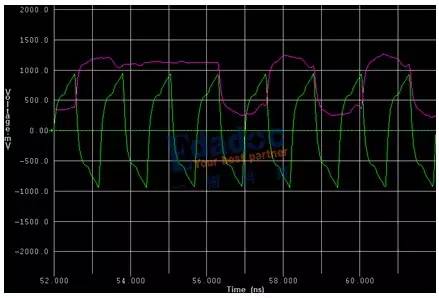

图2

上图2中,绿色的是时钟信号波形,紫色的是地址信号。可以看到,地址/命令,控制信号并不像时钟信号那样是周期性的,但它的位宽是时钟周期的整数倍,信号边沿都是要和时钟信号的下降沿对齐的,如果不能对齐,至少在时钟信号下降沿附近。

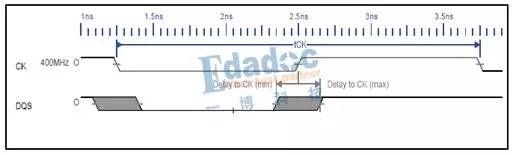

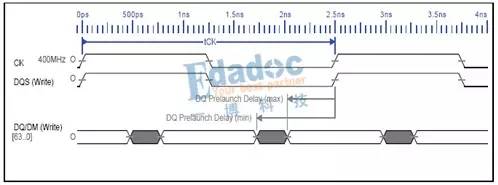

同样的,数据信号是参考DQS的,DQS又是参考时钟信号的,它们之间的位置关系如下图所示,图3是时钟信号与DQS之间的时序关系;图4是DQS与DQ之间的时序关系。

图3

图4

从上图可以看出,理想情况下,DQS的波形边沿与时钟信号的边沿是应该对齐的。对于数据信号来说,由于是DDR,双倍数据速率,时钟波形的上升沿和下降沿都能触发数据,为保证这一点,必须保证DQS信号波形边沿在DQ波形的中间位置。芯片工作时,这些相对位置都会出现一定的偏移,这些偏移量是芯片本身的属性,相关延时参数在芯片手册上可以查找。

理论联系实际,我们还是来看看芯片在实际工作的时候,这几组信号之间的相对位置是不是我们上面说的那样。

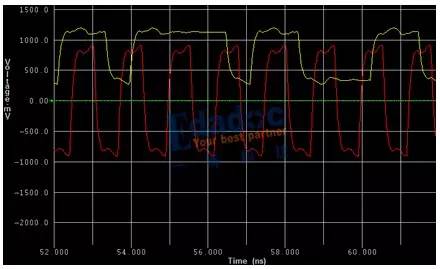

图5

上图中红色波形时DQS信号,黄色是数据信号,可见,数据信号在翻转的时候,边沿基本上都在DQS脉冲的中间位置,这也保证了接收端在读取信号的时候有充足的建立时间与保持时间。

综上所述,本篇文章定性的介绍了一下DDR各组信号之间的时序关系,没有做定量计算。在实际的时序仿真中,重点在于能够在芯片手册上找到这些时序参数,并理解这些时序参数的含义。最后通过评估建立时间与保持时间的裕量来判定系统时序是否符合要求。

最前沿的电子设计资讯

最前沿的电子设计资讯