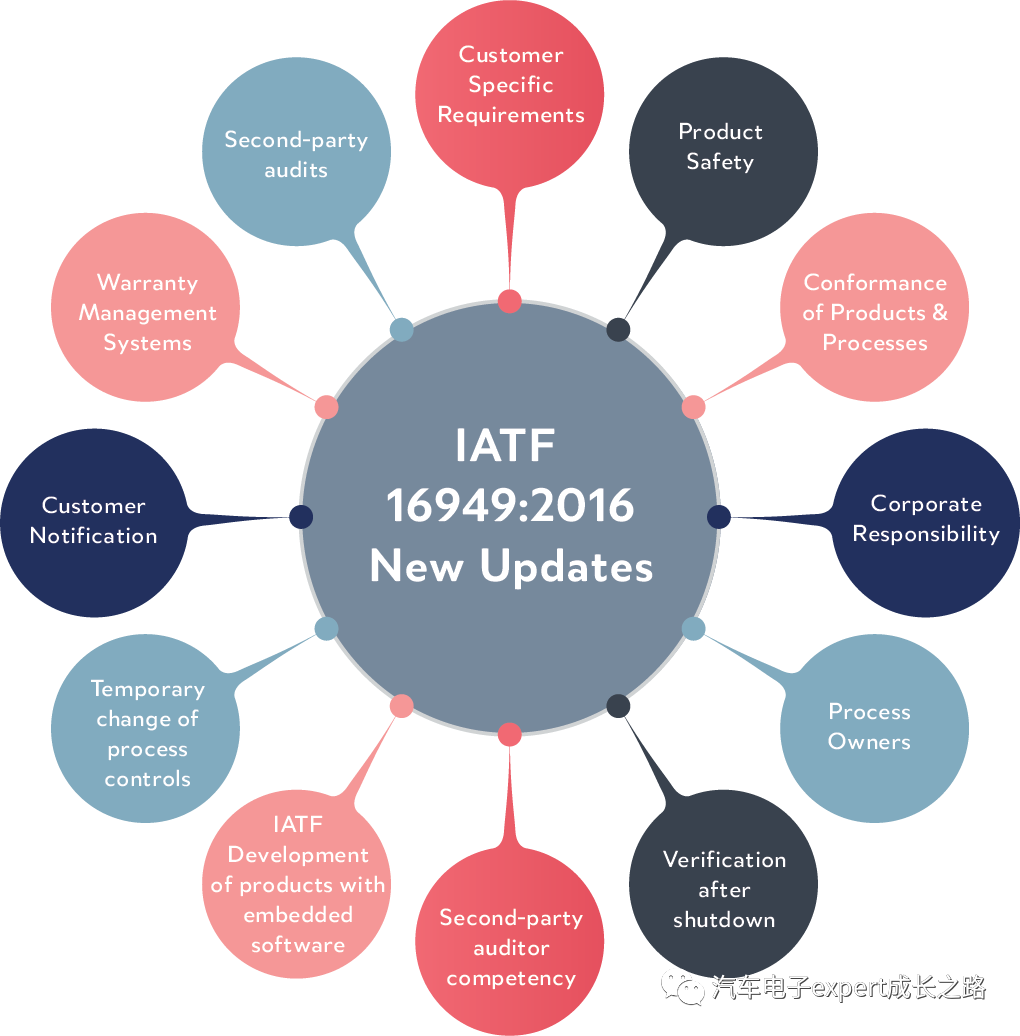

1.1 汽车行业铁律--IATF-16949

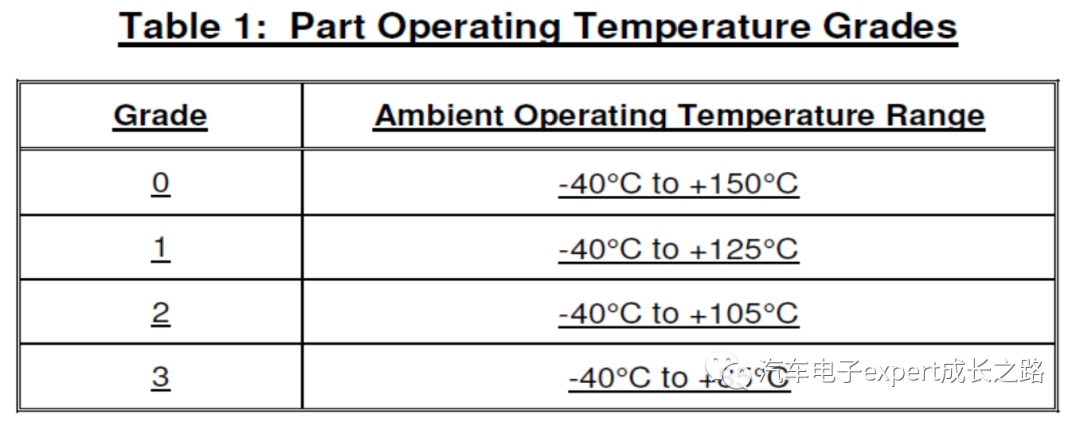

1.2 车规芯片可靠性验证标准--AEC-Q100

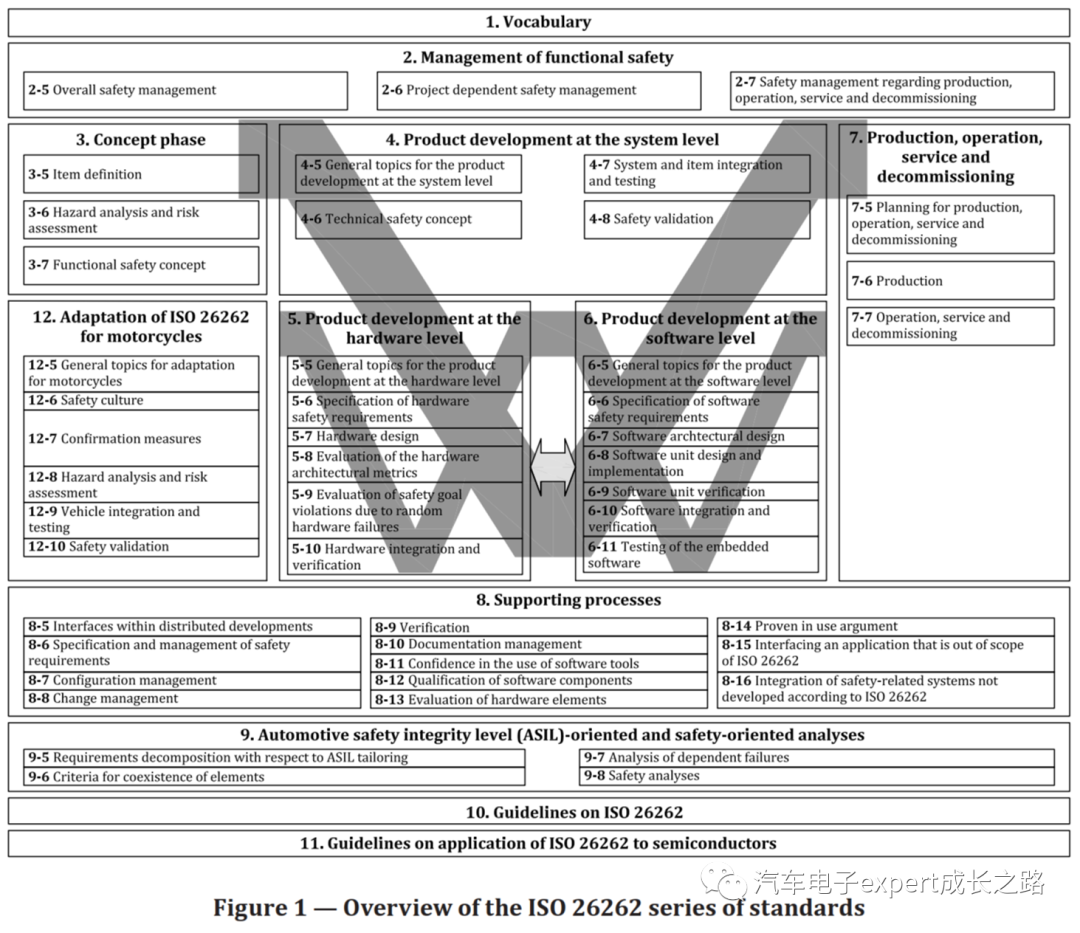

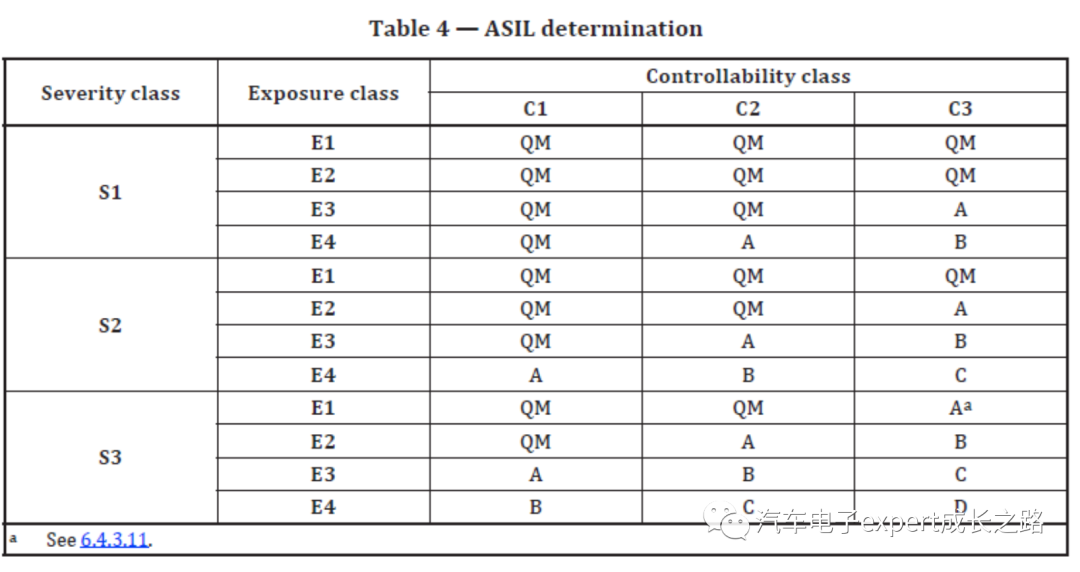

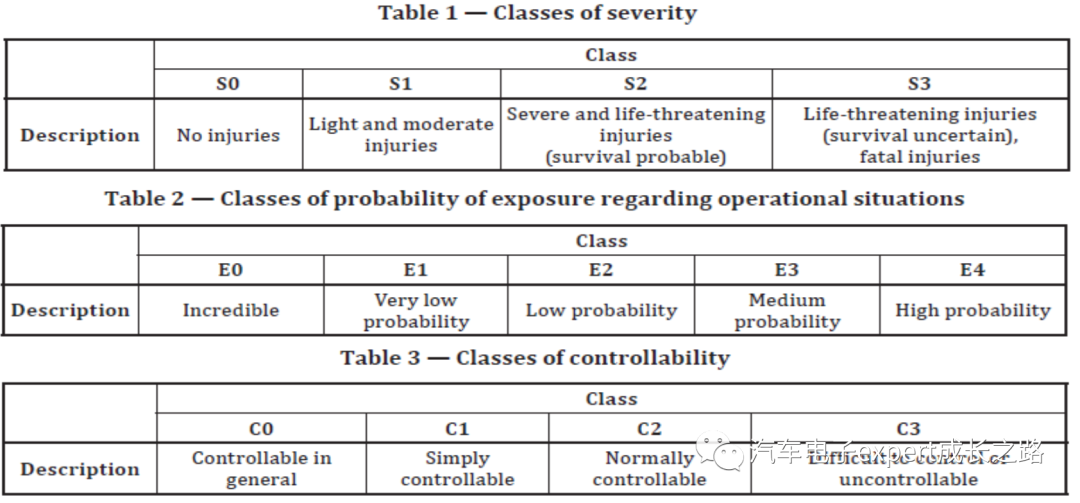

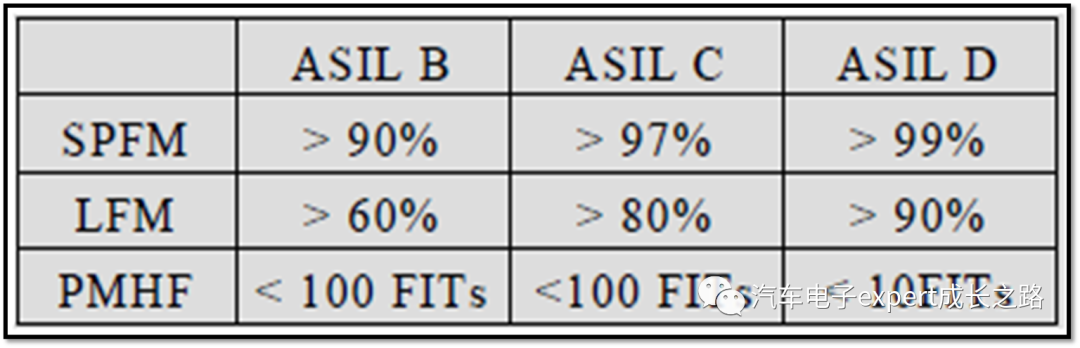

1.3 车规芯片功能安全标准--ISO 26262

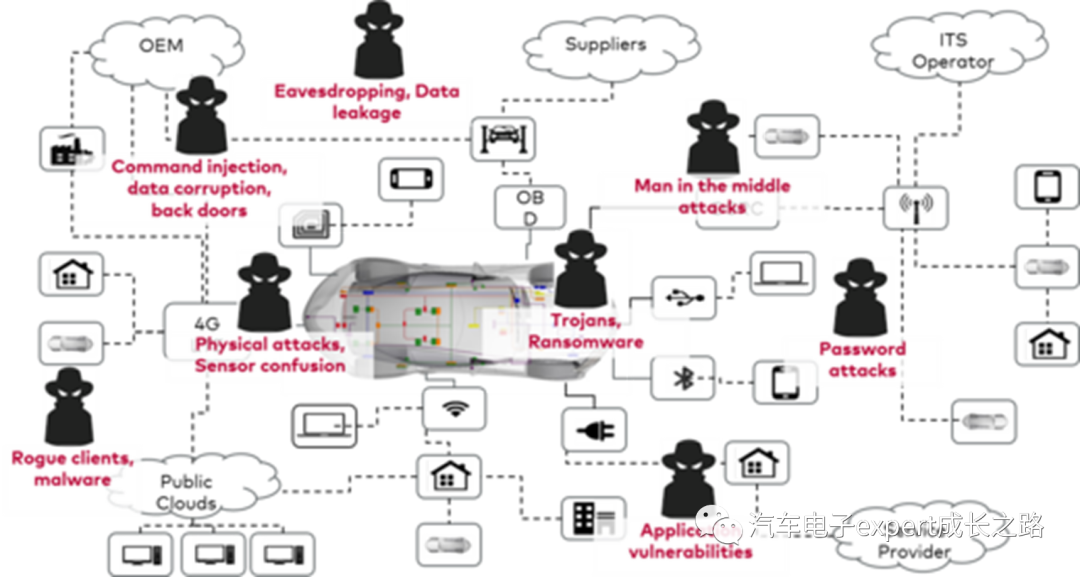

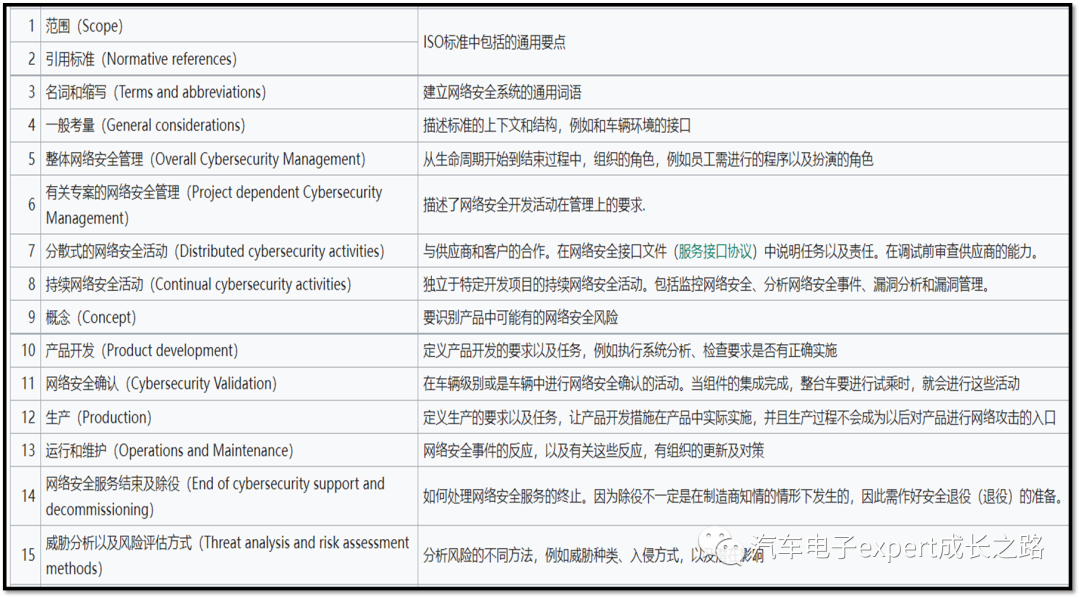

1.4 车规芯片信息安全标准--ISO 21434

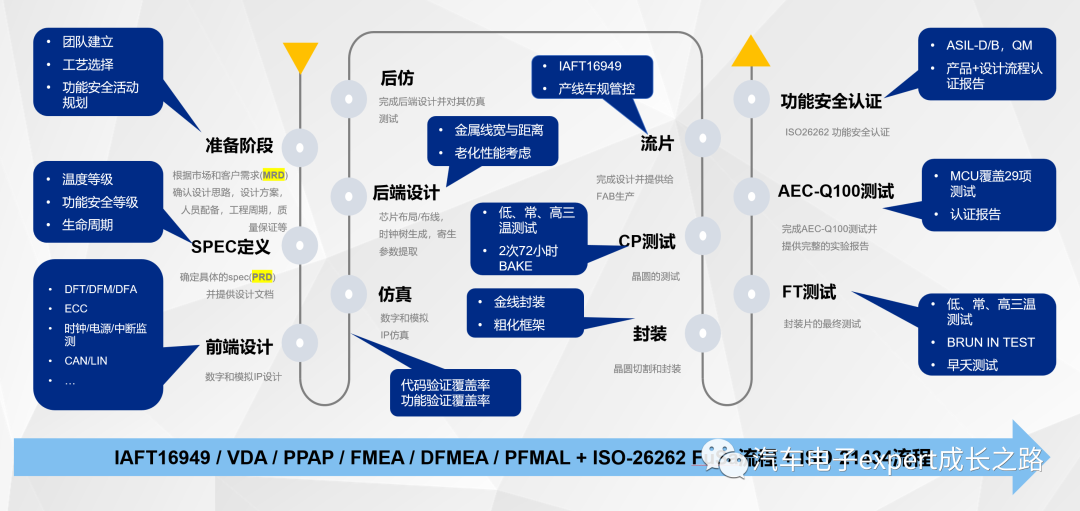

2.1 需求定义(MRD和PRD)

2.2 前端设计(数字外设和模拟外设IP设计)

2.3 逻辑仿真和数字验证

2.4 后端设计与仿真

2.5 流片与ECO设计修改

2.6 回片测试与EVB功能验证

2.7 CP测试

2.8 Bonding与封装

2.9 FT测试与老化测试(Burn-In)

2.10 AEC-Q100可靠性测试

2.11 小批量出货(SOP)

2.12 量产

2.13 售后质量分析(FA)

2.14 DFT与DFM

3.1 汽车软件开发流程--ASPIC与CMMI

3.2 汽车开放系统架构--AUTOSAR MCAL

3.3 软件开发工具链(Toolchain)

3.4 各种中间件软件(Middleware)

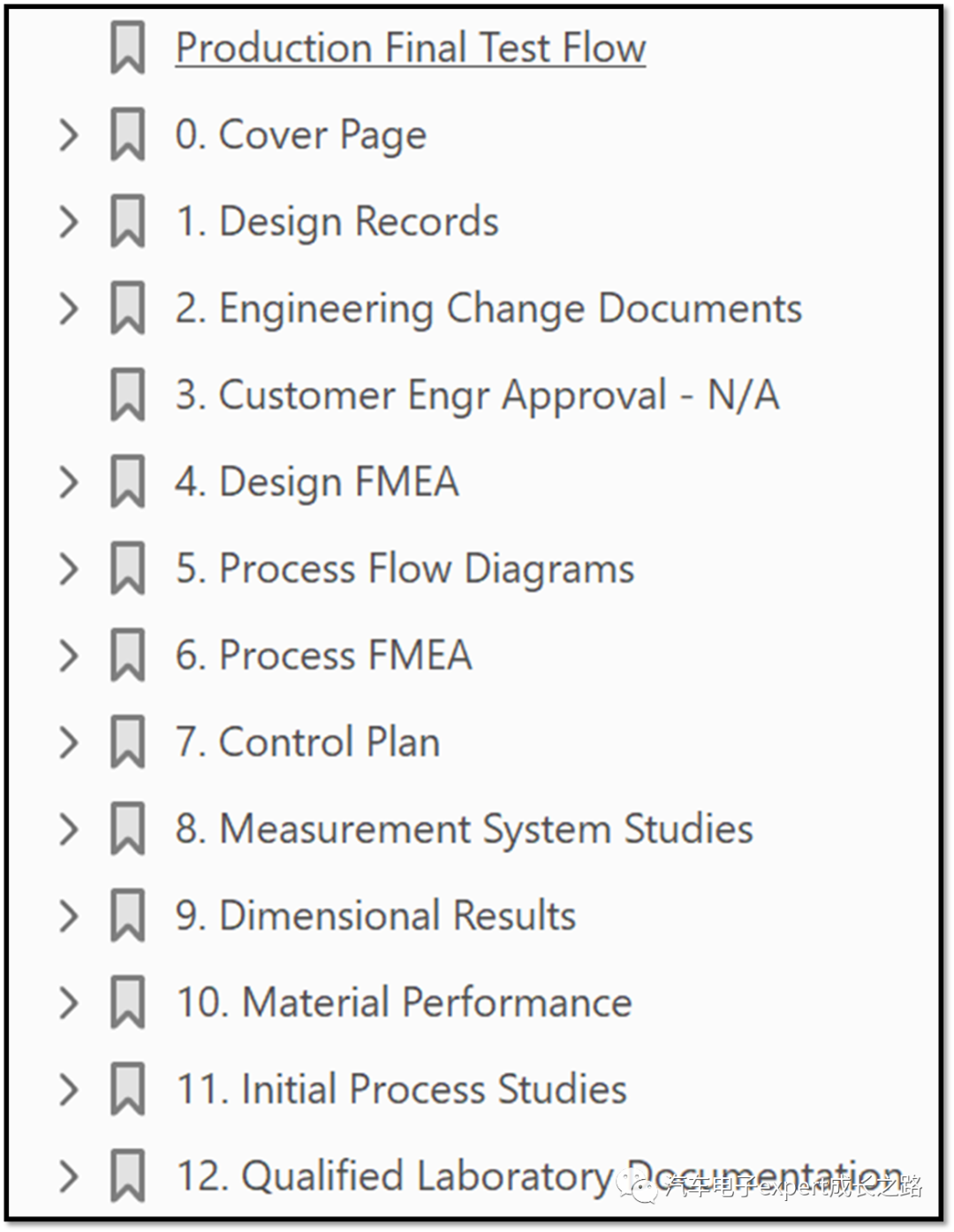

其中,PPAP报告是汽车产业链供应商逐级提供的,由晶圆厂和封测厂提供的PPAP被整合到车规芯片的PPAP中,然后提供给零部件设计生成商(Tier-1),最后由Tier-1整合ECU系统软硬件设计和生产的流程数据提供给整车厂。

CP测试是芯片制造过程中的一个重要环节,它可以帮助检测和排除芯片制造过程中的缺陷和问题,确保芯片的质量和可靠性。同时,CP测试也可以提供有关芯片的电气特性和功能的重要信息,为后续的封装和测试工作提供指导和依据。

最前沿的电子设计资讯

最前沿的电子设计资讯