传输线结构包括信号路径和返回路径,以平面形式出现的返回路径通常被称为参考平面。不少刚接触高速信号设计的朋友会有这样的困惑:都说走线的参考平面很重要,为啥有些信号还要把途经SMD元器件管脚下方的参考平面挖掉?挖掉就挖掉,不同单板反焊盘掏空的参考平面数量还不一样,就不能痛快点给个标准吗?

高速先生也想,但是,真没有。

今天,我们就以常见的0402封装AC耦合电容为例,说说为啥会这么折腾。

第一个问题,既然反焊盘处理这么麻烦,不挖行不行?必须满足大家,电容相邻的参考平面L2层不挖空!

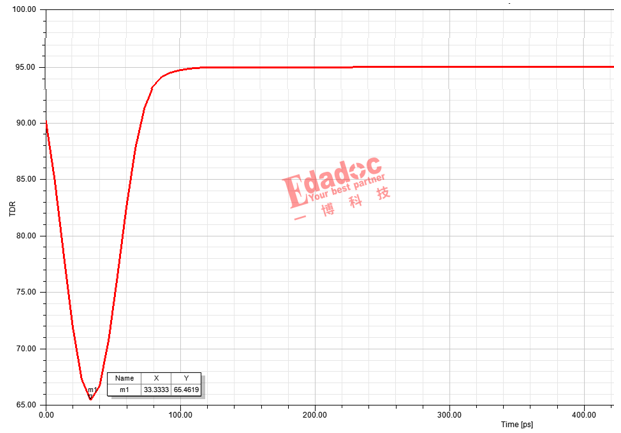

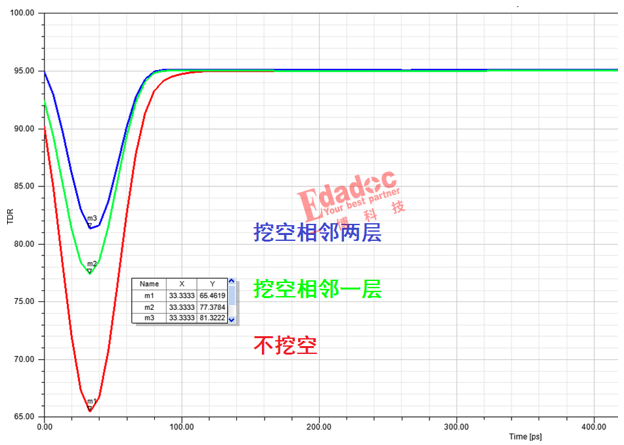

效果如何?直接上图(这里的差分走线阻抗控95欧姆):

阻抗控制95欧的信号,参考平面不挖空的电容位置阻抗直接掉到65欧!如果你是信号,你说烦不烦?

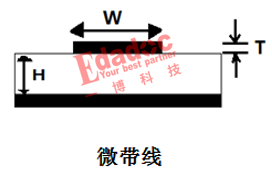

为啥出现这种现象?我们不妨把电容焊盘当成走线—— 一种很宽很宽的微带线,回忆一下传输线的理论,线宽越大,阻抗越小,况且,电容本体也有一定的高度,相当于铜厚的增加,所以,0402封装电容的阻抗跌成这样也就不难理解了。

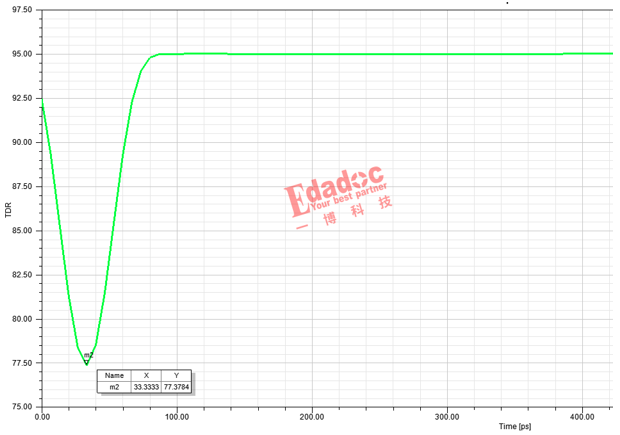

问题又来了,在层叠和电容封装确定的前提下,增加阻抗需要拉开到参考平面的间距H,怎么拉开?在参考平面挖反焊盘呗。那么要挖多少层呢?本案例中反焊盘的大小按照电容焊盘的尺寸,先挖一层试试。

效果立竿见影,挖空相邻第一个参考平面后,电容的有效参考平面就变成了相邻的第二个,H变大,阻抗也从65欧提高到77欧,还有比这更好用的方法吗?

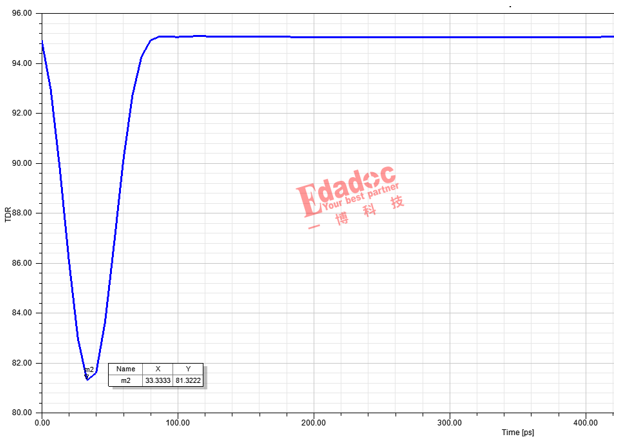

有,多挖一层看看。

挖空相邻两层参考平面后,间距H继续拉大,阻抗进一步提高至81欧。

虽然本文中的仿真数据对于其它单板未必适用,阻抗变化的趋势却是一致的。把上文提到的三种反焊盘处理的阻抗放在一起就一目了然了。

高速信号的布线关注阻抗的连续性,而途经SMD元器件管脚位置的阻抗通常偏小,与走线的特征阻抗不一致,为了尽量提高这些地方的阻抗,元器件管脚下方的参考平面需要进行反焊盘处理,增加管脚到有效参考平面的间距。但是,由于不同单板的层叠各异,元器件封装的大小不一,挖空的层数也不尽相同……

所以,到底该怎么挖反焊盘呢?这可能就是SI攻城狮存在的意义了。

最前沿的电子设计资讯

最前沿的电子设计资讯