这是下半部分CoWoS。

真正的瓶颈 - CoWoS

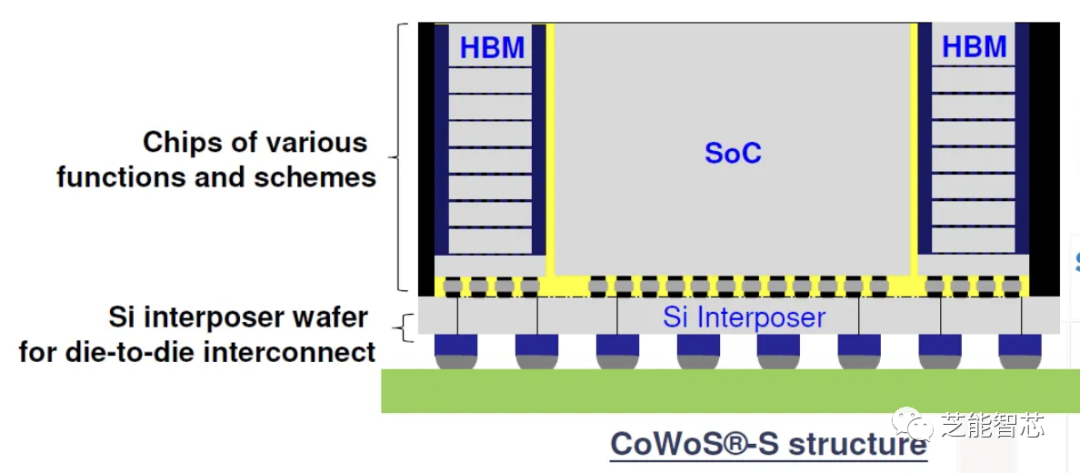

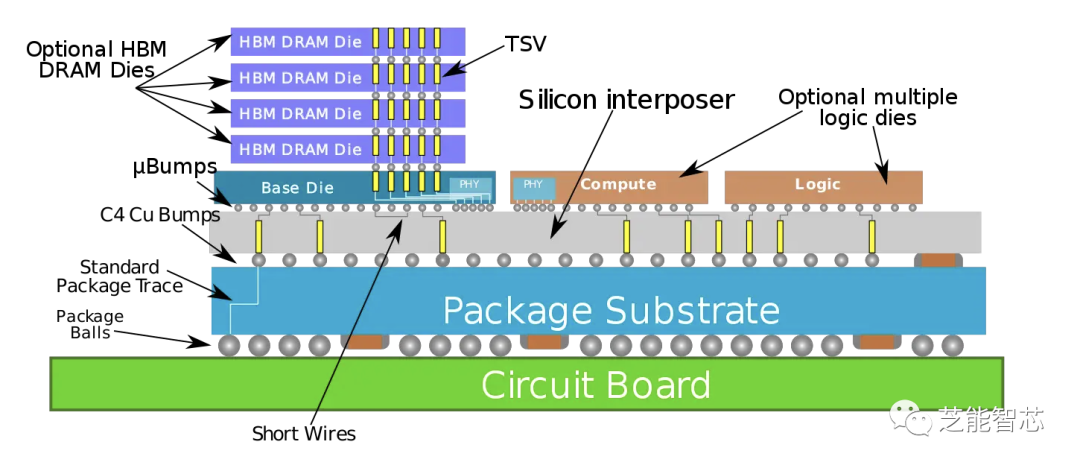

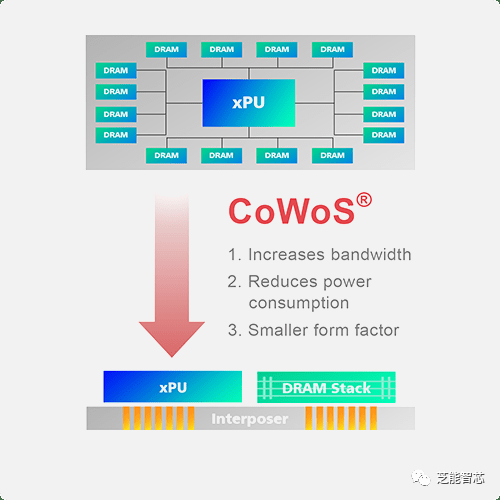

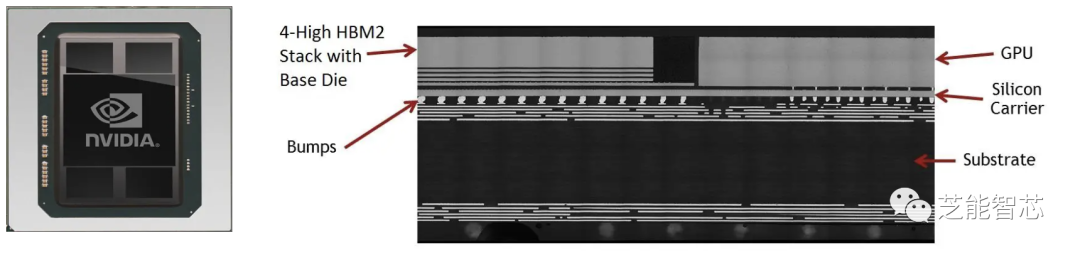

AI算卡的真正瓶颈是CoWoS容量,CoWoS(晶片封装在晶圆上)是台积电的一种“2.5D”封装技术,多个活动硅晶片(通常配置为逻辑和HBM堆栈)集成在被动硅插板上。

插板充当了顶部活动晶片的通信层,插板和活动硅然后附在一个包装基板上,其中包含将放置在系统PCB上的I/O

HBM和CoWoS是互补的,HBM的高垫片数和短距离跟踪的要求需要2.5D高级封装技术(CoWoS),以实现如此密集、短距离的连接,这是不可能在PCB甚至包装基板上完成的。

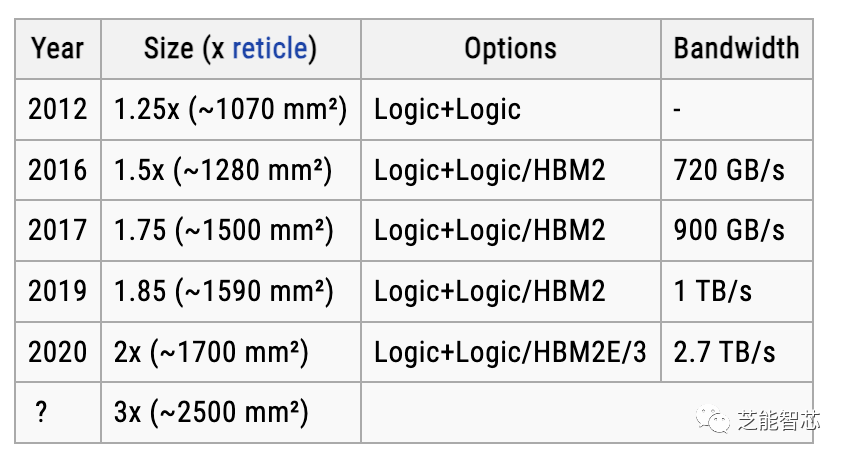

CoWoS是提供最高互连密度和最大封装尺寸的主流封装技术,成本也相对合理。由于几乎所有HBM系统都使用CoWoS进行封装,所有先进的AI加速器都使用HBM,因此几乎所有领先的数据中心GPU都由台积电在CoWoS上封装。

CoWoS是目前高性能计算领域唯一选择,即使HBM缺货的情况得以缓解,制约H100 GPU的真正因素仍然是CoWoS容量。CoWoS是一项非常复杂的制造工艺,涉及将多个芯片以精确的方式堆叠在一起,并要求极高的制造精度。全球只有少数几家公司能够提供CoWoS封装,台积电是最大的提供商之一。英伟达已经开始了H100 GPU的生产,但CoWoS容量限制了它们能够生产的数量。英伟达计划每季度出货超过40万个H100 GPU,但由于CoWoS容量的限制,可能无法达到这个目标。除了英伟达,其他公司也在竞相获取CoWoS容量。

谷歌的TPUv6(也许也是v7)已经在生产中,也使用了台积电的CoWoS技术。谷歌的TPU产品线主要用于云计算,而不是个人PC。这使得TPU在PC市场上的供应量相对较小,不太可能对英伟达的GPU产量构成威胁。由于CoWoS容量的稀缺性,一些公司正在考虑开发自己的CoWoS封装技术,以减轻制约。

GPU和HBM的生产瓶颈主要是由于CoWoS封装容量的限制。尽管TSMC和其他半导体制造商可以提供足够多的晶圆供应和HBM供应,但CoWoS技术的有限供应限制了GPU的实际生产能力。随着更多的公司考虑开发自己的CoWoS能力,未来可能会有一些改善,但这需要时间和投资。

最前沿的电子设计资讯

最前沿的电子设计资讯