此KWIK(Know-how With Integrated Knowledge——技术诀窍与综合知识)电路应用笔记提供了应对特定设计挑战的分步指南。本文将讨论与特定应用相关的要求,如何利用通用公式进行转换,以及如何轻松地将其扩展到其他相关的应用规格。

在电磁流量计或生物电测量等应用中,小差分信号与大得多的差分偏移串联。这些偏移通常会限制您在前端可以获取的增益,降低整体动态范围,尤其是在使用电池供电的较低电源电压的信号链上。

本指南将帮助您设计一个低功耗、交流耦合信号调理电路,该电路既能抑制大偏移电压,又能放大小的差分信号。此外,本指南将有助于围绕高通滤波器的增益级的划分以及噪声考虑因素。

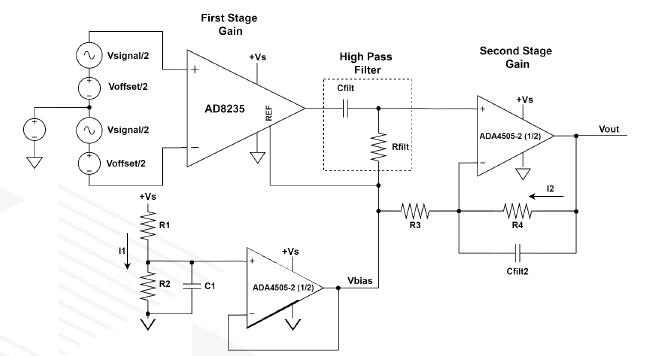

图1所示电路的设计选择在很大程度上取决于输入信号和偏移的幅度范围及频率,还有电源电压以避免饱和。功耗和尺寸对电池供电应用也很关键。示例设计规格如表1所示。

图1.电池供电的交流耦合信号调理电路

表1.图1所示电路的主要设计规格

| 传感器Voffset最大幅度Voffset | 传感器Vsignal最大幅度Vsignal | 传感器Vsignal最小/最大频率 | 传感器共模电压(Vcm) | 电源+Vs/-Vs | Vbias/输出共模电压 | 最大电源电流 |

| ±300mV | ±10mV | 0.5Hz/40Hz | 1.65 ±1V | +3.3V/0V | +1.65V | 100uA |

图1所示电路是一个交流耦合信号调理电路,可以采用最低3.3V单电源供电。图1中的电路从仪表放大器AD8235开始,它提供高输入阻抗、CMRR、最小5倍增益和差分至单端转换。接下来是一个高通滤波器(Cfilt、Rfilt),用于抑制放大的Voffset,然后是ADA4505,用于提供额外的增益和滤波(R4、R3、Cfilt2)。生成的Vbias用于将AD8235和ADA4505增益级输出共模均设置为中间电源电压(+Vs/2),因为Vsignal和Voffset都是差分信号。Vbias由分压器(R1、R2)生成,并由另一个ADA4505缓冲。AD8235和ADA4505-2均采用紧凑型WLCSP(晶圆级芯片规模封装),其总电源电流小于45uA(典型值),因此它们是该电池供电解决方案的出色选择。

设计技巧/注意事项

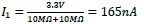

1.考虑电路的总电源电流时,电阻值R1、R2、R3和R4的选择也很重要。电阻选择是噪声与功耗的权衡结果。对于此电路,最好选择较大的电阻值以最大程度地减少额外的电源电流。电路中有两个地方需要额外的电源电流。I1为流经电阻分压器的电流: I2为流经第二级增益电阻的电流。为获得最大输出信号,增加的电源电流将是:

I2为流经第二级增益电阻的电流。为获得最大输出信号,增加的电源电流将是:

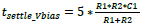

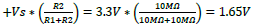

2.对于电阻分压器(R1、R2),可以增加一个电容C1以对噪声进行限带,并减少对+Vs的60Hz或其他干扰。电容越大,噪声滤波越好,但上电时Vbias将需要更长的时间才能稳定下来。建立到1%以内所需的时间估计为:

3.ADA4505缓冲器用于将Vbias驱动到图1所示电路的不同节点。AD8235的REF引脚上需要低阻抗驱动,因为该引脚的输入阻抗是阻性。任何额外的串联电阻都会降低CMRR并增加增益误差。缓冲器还会防止Rfilt和R3的加载效应。通过向Rfilt和R3提供相同的Vbias,没有放大这两个偏置点之间的直流差的风险。此外,这还会降低从Vbias到Vout的噪声贡献,因为相关噪声源会抵消。如果Vout相对于Vbias测量,而不是相对于地测量,上述噪声贡献还能进一步降低。

4.虽然直流规格不会对这样的交流耦合解决方案产生重大影响(误差远小于传感器Voffset),但在设置最大输出摆幅范围时应加以考虑,因为直流规格会增加总差分输入摆幅。需要考虑的直流规格包括失调电压和任何流经AD8235的传感器阻抗以及流经ADA4505的Rfilt、R3、R4的输入偏置电流。设计的目标温度范围也可能增加这些直流误差。如果总差分输入摆幅变得太大,以至于第一或第二增益级存在饱和的风险,那么可以通过降低增益或提高电源电压+Vs来解决此问题。任何+Vs电源变化也应予以考虑。

5.确保输入/传感器的偏置位于AD8235的输入共模范围内。这是一个单电源解决方案,鉴于共模输入电压与输出范围的关系或“钻石图”,大多数仪器放大器的最优值位于中间电源电压(+Vs/2)。此共模电压可以由第三电极提供,例如生物电势应用。下面的设计仿真部分将介绍一种对此有帮助的仪表放大器钻石图工具。

6.交流耦合选择在图1所示位置而不是输入端,有两个重要原因。当交流耦合在输入端时,两个输入端都需要滤波器来保持电路的差动平衡,因此这些元件的容差会影响滤波器的匹配程度,并会降低共模抑制相对于频率的性能。此外,所选的电阻会限制输入阻抗。有关这两个电路的示例比较,请参见附录。

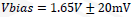

1.设置Vbias:

为使电源电流贡献小于1uA,设置R1 = R2 = 10MΩ。

ADA4505之前的电阻分压器的输出:

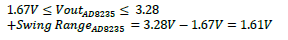

使用容差小于1%的R1和R2,将使Vbias变化保持较低水平,有助于最大程度地提高第一和第二增益级的输出摆幅。结合1%电阻和ADA4505缓冲器的Vos:

为了消除电阻的交流电源干扰和噪声,设置C1使得截止频率至少小于Vsignal最低频率0.5Hz。在这种情况下,C1设置为0.1uF:

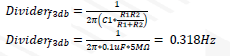

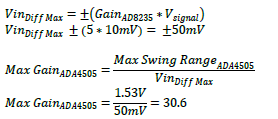

2.设置第一级增益

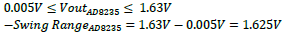

首先,考虑AD8235输出摆幅范围对供电轨的限制。对于给定电源电压,这些值可以从数据手册的“高输出电压”和“低输出电压”部分找到。这种情况下没有阻性负载,保守起见,我们使用100kΩ摆幅的最差情况:

由于输入是全差分式,因此就Vbias而言,这将是最差情况输出摆幅。

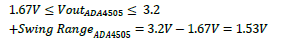

对于正输入信号(Vbias_max=1.67V):

对于负输入信号(Vbias_min=1.63V):

现在为了设置增益,计算总预期差分输入信号,并使用正负摆幅范围的下限来设置最大摆幅范围:

没有外部Rg电阻时,AD8235的最小增益为5,因此我们使用此值,从而为直流误差和其他情况留一些裕量。另外,必须检查选定增益情况下的“钻石图”。有关此操作,请参见设计仿真部分。

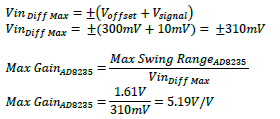

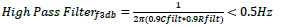

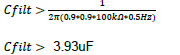

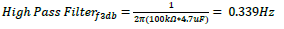

3.设置高通滤波器

假设Rfilt和Cfilt的元件容差为±10%,最快时间常数应小于Vsignal最低频率:

如果选择Rfilt=100kΩ并重新整理方程:

采用最接近的标准电容值,设置Cfilt = 4.7uF,那么更新后的标称截止频率为:

如果设计规格需要对最小信号频率进行某种最低衰减,则很容易检查给定滤波器的截止频率。请参见此电路的示例:

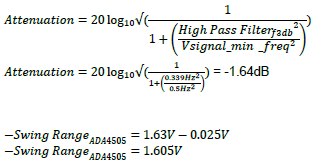

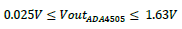

现在为了设置增益,计算ADA4505输入端的总预期差分输入信号,并使用正负摆幅范围的下限来设置最大摆幅范围:

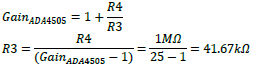

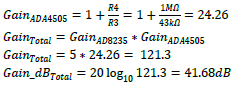

我们采用大约25倍的增益,以为直流误差和其他元件容差留一些裕量,并选择R4 = 1MΩ,以在最大信号摆幅时保持较低电源电流。

将R3四舍五入到下一典型电阻值,得到43kΩ。

4.设置第二级增益

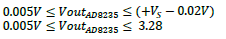

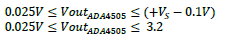

使用类似于第一级增益的方法,首先根据数据手册确定ADA4505输出摆幅范围限值。阻性负载未知,保守起见,我们将使用10kΩ最差情况:

由于输入是全差分式,因此就Vbias而言,这将是最差情况输出摆幅。

对于正输入信号(Vbias_max=1.67V):

对于负输入信号(Vbias_min=1.63V):

5.利用Cfilt2设置低通滤波器

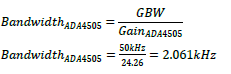

首先使用增益带宽积(GBP)确定ADA4505在24.26倍增益下的带宽:

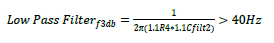

如果目标带宽因为预期最大信号频率而需要进一步降低,以及/或者需要限制宽带噪声,那么可以使用电容Cfilt2。假设R4和Cfilt2的元件容差为+/-10%,最慢时间常数应大于Vsignal最大频率

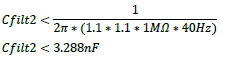

使用1MΩ的R5,重新整理方程:

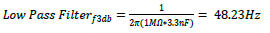

然后可以将其四舍五入到最接近的标准电容值3.3nF,因此更新后的截止频率为:

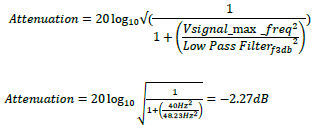

如果设计规格需要对最大信号频率进行某种最低衰减,则很容易检查给定滤波器的截止频率。

请参见此电路的示例:

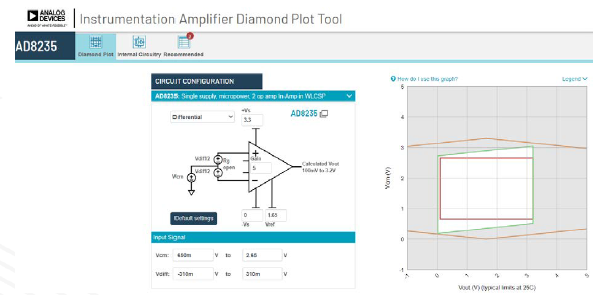

为了检查仪表放大器的共模输入范围与输出电压的关系或“钻石图”,您需要提供电源电压+Vs、基准电压、增益、共模摆幅和差分输入摆幅。ADI公司的仪表放大器钻石图工具可帮助了解输入摆幅是否在器件的工作范围以内。请注意,该工具使用的输出摆幅使用最差情况的负载条件(最小阻性负载)。因此,如果按照该工具的限值进行设计,则对于较大阻性负载,系统将会有更多裕量。

查看图2中的结果,绿色轮廓是在给定电源电压、输出摆幅、输入共模范围和器件基准电压下AD8235的可用范围。红色轮廓显示了对于给定的共模和差分输入模式摆幅,您使用了多少可用范围。目标是让红色轮廓保持在绿色轮廓以内。如果某些条件违反了此要求,工具将显示错误并提供建议。为了进一步了解仪表放大器内部发生的事情,“Internal Circuitry”(内部电路)选项卡会显示内部节点的电压。

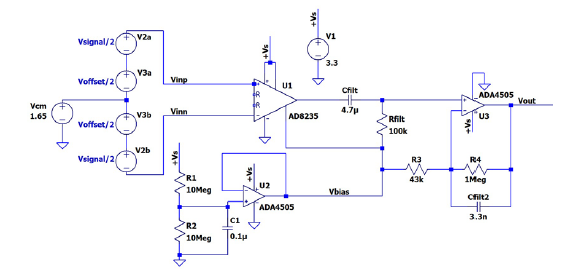

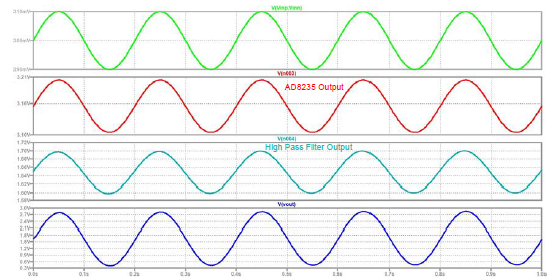

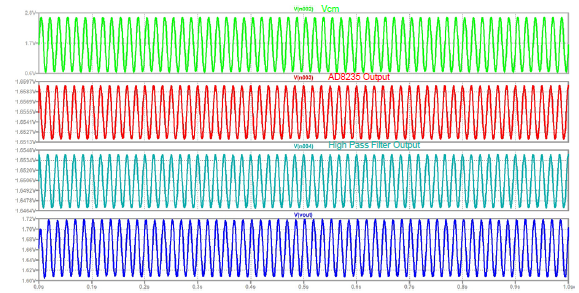

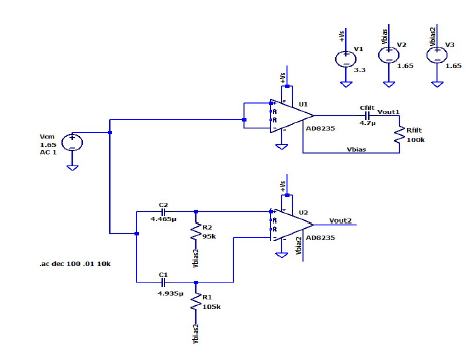

LTspice是一款出色的仿真工具,可用来检查上文进行的设计过程计算,包括其他有意义的规格,例如目标信号频带的噪声性能。LTspice原理图如下图3所示。第一个仿真是瞬态仿真,直流偏移为300mV,输入信号为±10mV (5Hz)。图4显示了电路中各级的信号。绿色曲线是总差分输入信号。红色曲线是AD8235输出端的放大后信号。蓝绿色曲线显示了移除直流偏移后的高通滤波器输出,最后的蓝色曲线显示了最终的放大后5Hz信号。

图2.AD8235钻石图工具示例

图3.LTSPICE原理图

图4.在电路不同级进行的瞬态仿真,Voffset=300mV,Vsignal=±10mV

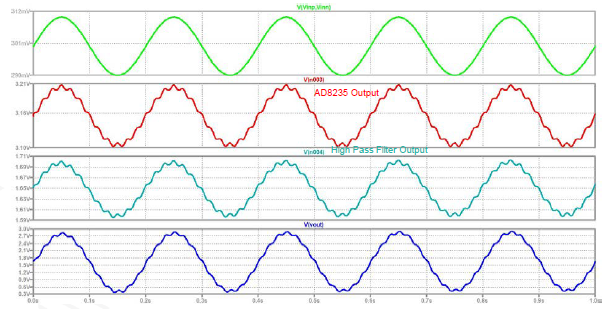

图5使用严苛的2Vp-p 60Hz Vcm输入信号(绿色),而未施加任何差分信号。在电池供电的应用中,60Hz信号达到如此高的电平是不太可能的,但这是需要考虑的事情。请注意,图中的所有信号都位于Vbias = 1.65V的直流电压。大部分衰减来自AD8235的CMRR,其在60Hz时大于60dB(红色和蓝绿色曲线~7.5mVp-p)。最终输出(蓝色曲线~110mVp-pk)经放大后,由48Hz低通滤波器部分衰减。

图6显示了如果共模和差模输入同时存在,信号将是什么样子。可以看到,60Hz信号作为纹波出现在已被放大的较慢5Hz信号之上。图7显示,对于图4中的仿真设置,来自+Vs的电源电流小于52uA。

图5.在电路不同级进行的瞬态仿真,Vcm=1.65V±1V

图6.在电路不同级进行的瞬态仿真,Voffset=300mV,Vsignal=±10mV,Vcm=1.65V±1V

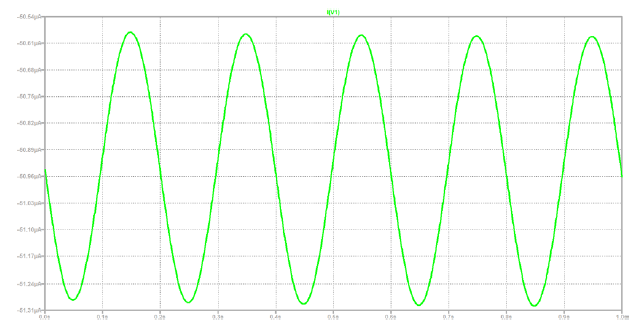

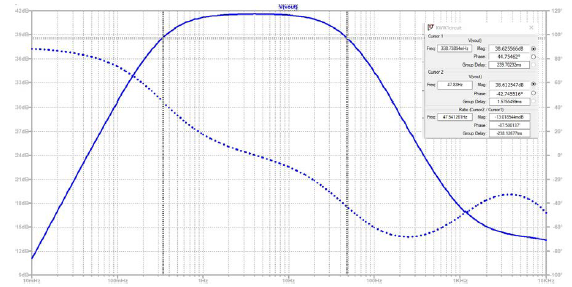

图8中的另一个仿真显示了图3中电路的频率响应。峰值幅度是在5Hz频率确定的,光标1和2分别放置在高通和低通滤波器的-3dB点。下表显示了计算结果与测量结果的比较。

表2 - 计算结果与仿真结果

| 规格 | 计算 | 仿真 |

| 增益_dB总 | 41.68dB | 41.6dB |

| 高通滤波器f3db | 0.339Hz | 0.339Hz |

| 低通滤波器f3db | 48.23Hz | 47.88Hz |

在频率响应中,值得一提的是对于此电路中使用的低通滤波器,当Cfilt2短路时,第二级的增益降至1。这意味着,来自AD8235和高通滤波器的信号在达到AD8235的带宽之前不会继续衰减。为了进一步滤波,可以将一个低通滤波器放在第二增益级的输出端,就像通常在ADC之前所做的那样。

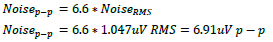

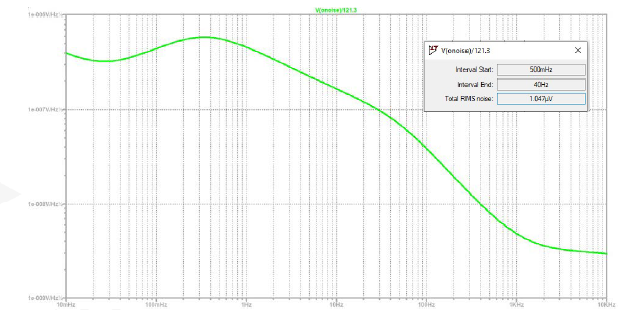

图9中的另一个仿真显示了图3中电路的电压噪声密度与频率的关系(折合到输入)。做法是将输出噪声除以解决方案的总增益(121.3)。使用有效值噪声计算器来计算从0.5Hz到40Hz(即目标Vsignal频率范围)的积分噪声。要使用此计算器,首先右键单击图形的x轴以设置目标频率范围,然后按住Ctrl键并左键单击波形名称(V(onoise)/121.3)。使用下式可轻松将有效值噪声转换为峰峰值噪声:

快速检查AD8235噪声,确定这是主要的噪声源。这是有道理的,因为电路中的所有其他噪声源都是在第一级增益之后,折合到输入端的总噪声贡献得以减少。

图7.总电源电流的瞬态仿真,Voffset=300mV,Vsignal=±10mV

图8.图3中电路的频率响应

图9.图3中电路的电压噪声密度与频率的关系(折合到输入)

表3 仪表放大器

| 产品型号 | 封装尺寸(WLCSP) | Ibias (A)最大值 | Vos (V)最大值 | 增益最小值/最大值(V/V) | 0.1至10Hz噪声(uV p-p)典型值 | Vnoise(nV/rt-Hz)典型值 | Iq (A)典型值 | +Vs范围最小值/最大值(V) |

| AD8235 | 1.57 mm x 2.04mm | 50p | 2.5m | 5/200 | 4 | 76 | 30u | 1.8/5.5 |

表4:运算放大器

| 产品型号 | 封装尺寸(WLCSP) | Ibias (A)最大值 | Vos (V)最大值 | GBP (kHz)典型值 | 0.1至10Hz噪声(uV p-p)典型值 | Vnoise(nV/rt-Hz)典型值 | Iq/放大器(A)典型值 | +Vs范围最小值/最大值(V) |

| ADA4505-2 | 1.42mm x 1.42mm | 2p | 3m | 50 | 2.95 | 65 | 7u | 1.8/5 |

钻石图工具是一个网络应用程序,可生成特定配置的输出电压范围与输入共模电压关系图,也被称为钻石图,适用于ADI仪表放大器。

LTspice®是一款高性能SPICE III仿真软件、原理图采集工具和波形查看器,集成增强功能和模型,简化了开关稳压器、线性稳压器和信号链电路的仿真。

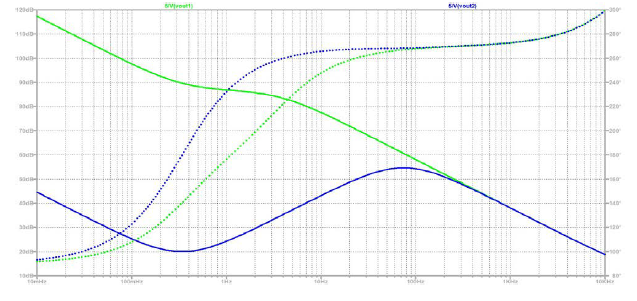

图10显示了LTSPICE原理图,其中比较了在输入端交流耦合的构想与在AD8235输出端交流耦合的做法。使用了相同的滤波器截止频率,但对于输入滤波器使用最差情况5%容差不匹配。共模与频率的关系图(折合到输入)如图10所示,其中比较了图1中电路(Vout1,绿色曲线)与前方的交流耦合(Vout2,蓝色曲线)。该结果未考虑传感器的任何其他不平衡(例如电极),也未考虑电容的ESL和ESR。

图10.交流耦合电路的比较(AD8235之前和之后)

图11.图10所示电路的CMRR与频率关系图的比较

# # #

Analog Devices, Inc. (NASDAQ: ADI)是全球领先的半导体公司,致力于在现实世界与数字世界之间架起桥梁,以实现智能边缘领域的突破性创新。ADI提供结合模拟、数字和软件技术的解决方案,推动数字化工厂、汽车和数字医疗等领域的持续发展,应对气候变化挑战,并建立人与世界万物的可靠互联。ADI公司2022财年收入超过120亿美元,全球员工2.4万余人。携手全球12.5万家客户,ADI助力创新者不断超越一切可能。更多信息,请访问。

最前沿的电子设计资讯

最前沿的电子设计资讯