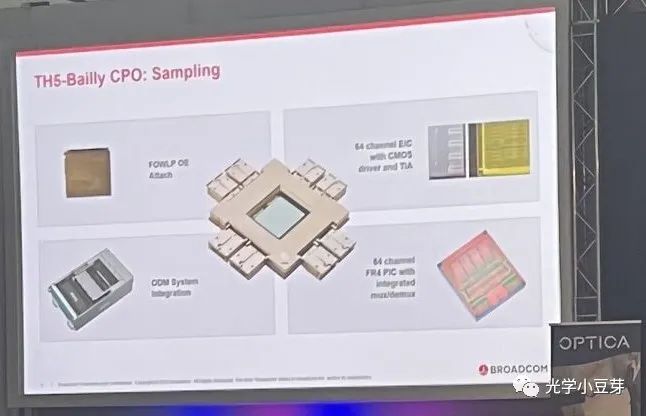

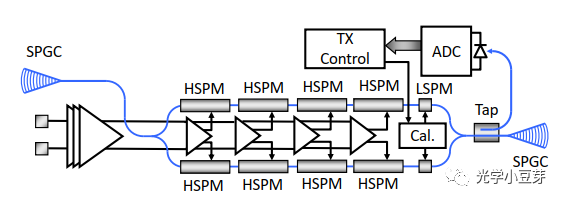

前面根据ECTC 2023的会议文章,介绍了Broadcom的CPO技术(Broadcom的CPO进展)。但文中的CPO产品并不是Broadcom最新一代CPO,最近凑巧在Linkin上划水时看到了一张图片,涉及到了博通最新一代51.2T CPO产品的一些技术细节,这里和大家分享一下。

图片不是特别清晰,但是信息量比较丰富。新一代CPO产品主要有四个特色,

1)FOWLP OE Attach

2)ODM System Integration

3)64 channel EIC with CMOS driver and TIA

4)64 channel FR4 PIC with intergrated mux/demux

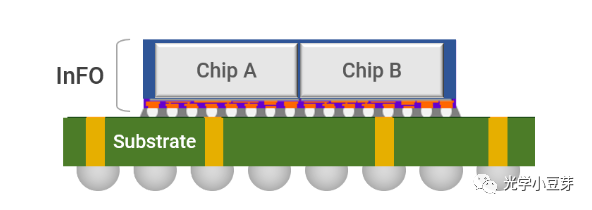

首先,在新一代CPO产品中,光引擎的封装方案由EIC的TSV last方案,更改为更加成熟的FOWLP方案。FOWLP的全称是fanout wafer level packaging。它是一种2.5D封装方案,可以将多颗芯粒集成到同一个封装内,如下图所示, 也称为INFO (Integrated Fanout)。FOWLP技术原本是为了解决随着芯片面积的减小和I/O接口数的增多,导致芯片内无法提供足够多空间放置I/O接口的难题。将多颗芯片同时放置在一个carrier wafer上,通过molding形成新的晶圆,再借助RDL层,将芯片内的IO接口引出(fan out)到芯片之外, 实现了更高的I/O密度。

(图片来自https://3dfabric.tsmc.com/japanese/dedicatedFoundry/technology/InFO.htm)

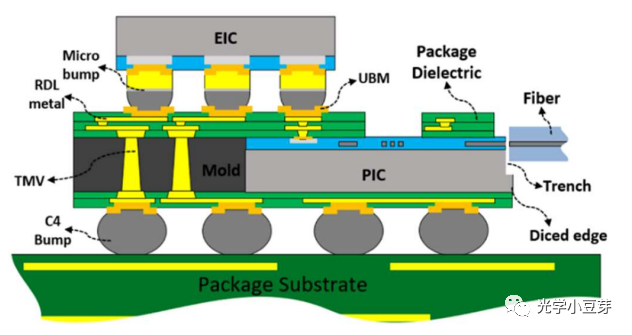

Broadcom没有给出具体的EIC和PIC封装结构图,小豆芽找到了新加坡IME的硅光芯片采用FOWLP封装方案的一张图片,可以对照参考下。借助FOWLP技术,在molding中制作VIA,同时给EIC和PIC供电。在FOWLP流程中,需要对edge coupler区域做特殊保护。

(图片来自文献1)

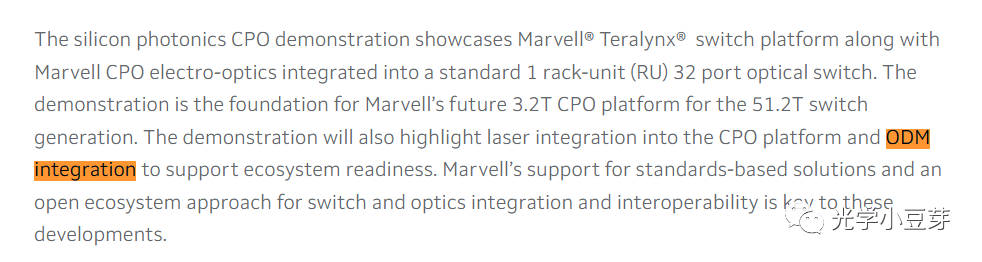

ODM的全称是original design manufacturer, 关于ODM system integration, Marvell在其CPO产品中也有类似描述,通过与ODM厂商合作,从而得到CPO生态系统的支持。这一点更多的是商业上的考虑。

单颗PIC中含有64个通道,单通道速率为100Gbps。单颗光芯片上集成了64通道,凸显了硅光在集成度上的优势,但对芯片的良率带来了更严苛的要求。由于通道数较多,如果仍然采用单波长方案,对应的光纤数将超过130根,不利于光学封装。因此,Broadcom采用了片上集成的Mux/DeMux设计,单个端口中含有CWDM4四个波长的信号,大大减小了光纤数目。简单估计下,Tx输出和Rx输入端共需32个光口,此外一个DFB可以支持4通道,激光器输入需要16个端口,光学封装仍然很有挑战。硅光片上集成的DeMux,一直是行业的难点,Intel和Luxtera的产品中都是采用外置的DeMux器件,华为采用了基于SiN波导的方案。Broadcom应该也是采用类似的方案。

与光芯片配套的电芯片,采用了CMOS工艺,这对driver的输出摆幅带来了限制,不像采用BiCMOS工艺的商用driver芯片,可以提供3-4Vpp的输出。相应地,对硅光调制器的设计也带来了挑战。小豆芽推测,Broadcom大概率是采用的segmented MZM设计,而不是传统的TWMZM设计,如下图所示。对应的分布式driver设计难度也较大,需要严格控制好延迟。采用Segmented-MZM设计,单通道信号速率有望进一步提高,达到200Gbps。Luxtera也是采用类似的Segmented-MZM设计。

(图片来自文献2)

根据官网给出的数据,新一代CPO的功耗为5.5W/800G, 对应能效比为6.8pJ/bit,性能非常优秀,这是整个系统协同设计优化的结果。Broadcom的CPO团队包括150多名工程师,不同专业领域的工程师集团化作战,具体细节可以参看其官网的介绍,链接如下https://www.broadcom.com/blog/broadcoms-persistent-cadence-copackaged-optics-innovation。

以上是基于Broadcom一页ppt的一些猜想与分析,可能与实际方案有一定出入,仅供大家参考,也欢迎大家留言讨论与指正。整体来说,Broadcom在芯片封装方案上选取了更加成熟、利于量产的FOWLP方案,而在光电芯片的设计上,选取了更具挑战的方案,单片集成了64个通道,而且实现了片上的DeMux。下一步,Broadcom会往单波200Gbps速率努力,从而实现102.4T的CPO产品。

文章中如果有任何错误和不严谨之处,还望大家不吝指出,欢迎大家留言讨论。

参考文献:1. S. Gourikutty, et.al., "A Heterogeneously Integrated Wafer-level Processed Co-Packaged Optical Engine for Hyper-scale Data Centres ", ECTC 2023

2. P. Dobbelaere, “Silicon photonics platform for high volume manufacturing”

最前沿的电子设计资讯

最前沿的电子设计资讯