EuTednc

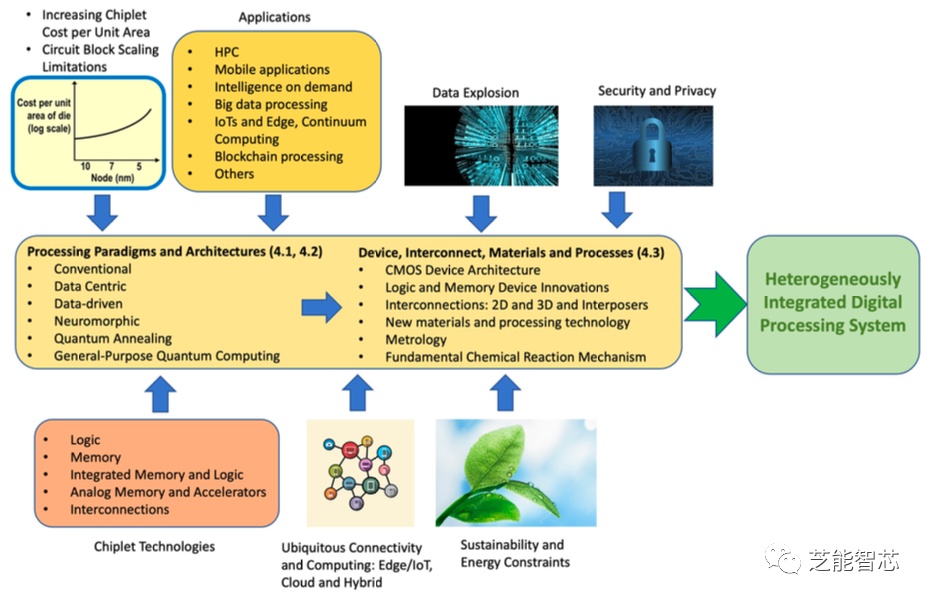

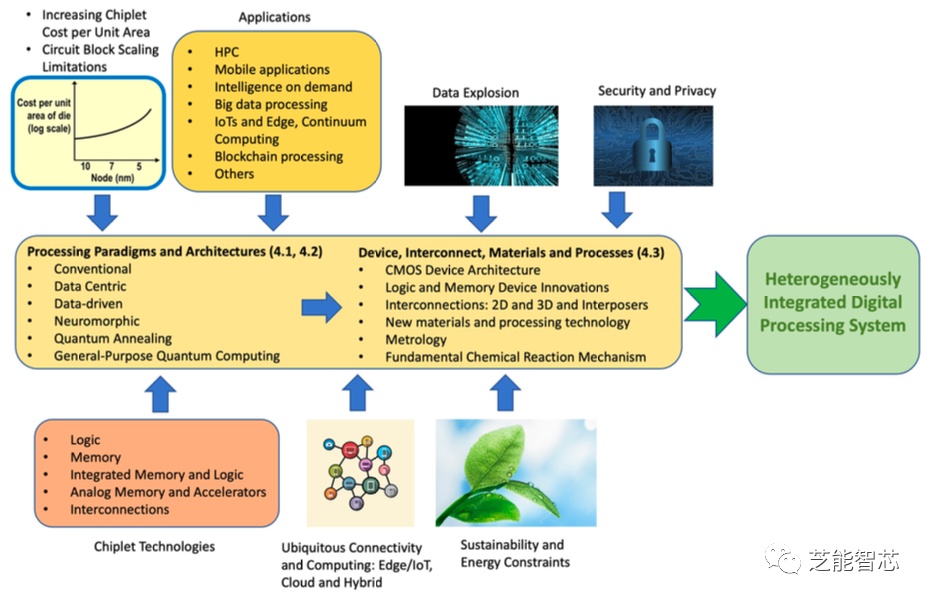

数字处理技术的路线图探讨了当前和新兴的数字处理驱动因素,以及处理范式中所需的创新。这些要求决定了数字处理、内存、支持芯片、互联、以及整体系统架构所需的技术和架构。主要分为三部分EuTednc

EuTednc

● 芯片和互连架构定义了设备、互连,以及化学和化学处理技术的要求。

● 化学处理需要对物理和化学反应机制有深入的了解,整合到产品中。

● 系统级集成数字处理系统所需的附加要求和解决方案,以及与整体安全性、功率转换/传递、系统可靠性和运行时管理需求相关的系统级考虑。

EuTednc

EuTednc

EuTednc

主要障碍和挑战 在实现异构集成数字处理系统时,需要解决一些障碍和挑战,包括: EuTednc

● 解决数据移动的成本问题,包括性能(延迟和带宽)和随着数据量和速率呈指数增长而增加的每比特传输的总能量消耗。

● 限制系统级别的总能量消耗,极大提高数字处理系统的能效,以处理数据洪流和对此类数据的必要处理。

● 解决当前使用的架构和系统中的系统级封装(SiPs)所固有的缩放限制,这些限制受到总功率、功率分配、中间层和互连的影响。改善未来设备制造的物理和化学过程的基本理解,包括先进图案制备、原子尺度薄膜沉积、刻蚀、区域选择性沉积和其他选择性材料处理。

● 解决异构集成数字处理系统日益增长的安全性和可靠性需求,包括监视和解释所有必要信息以确保安全和可靠操作。

● 解决并改善端到端的可持续性,包括前期设计、设计、制造、使用和最终处理/回收。

● 提供高级设计工具,允许将功能解聚为多芯片体系结构,并在多个参数之间进行同时优化;在需要探索的大型设计空间中进行优化提出了需要基于机器学习的解决方案的挑战。

接下来需要分三部分来讲解EuTednc

● 第一部分讨论应用需求如何推动数据处理范式

● 第二部分讨论了这在系统级别的体系结构上产生的影响,以及相关的挑战、实施和技术需求。

● 第三部分系统级体系结构需求转化为设备、互连、材料和化学处理挑战,以及有望的解决方案。

数字处理范式、系统级架构和数字处理设备/材料的路线图 EuTednc

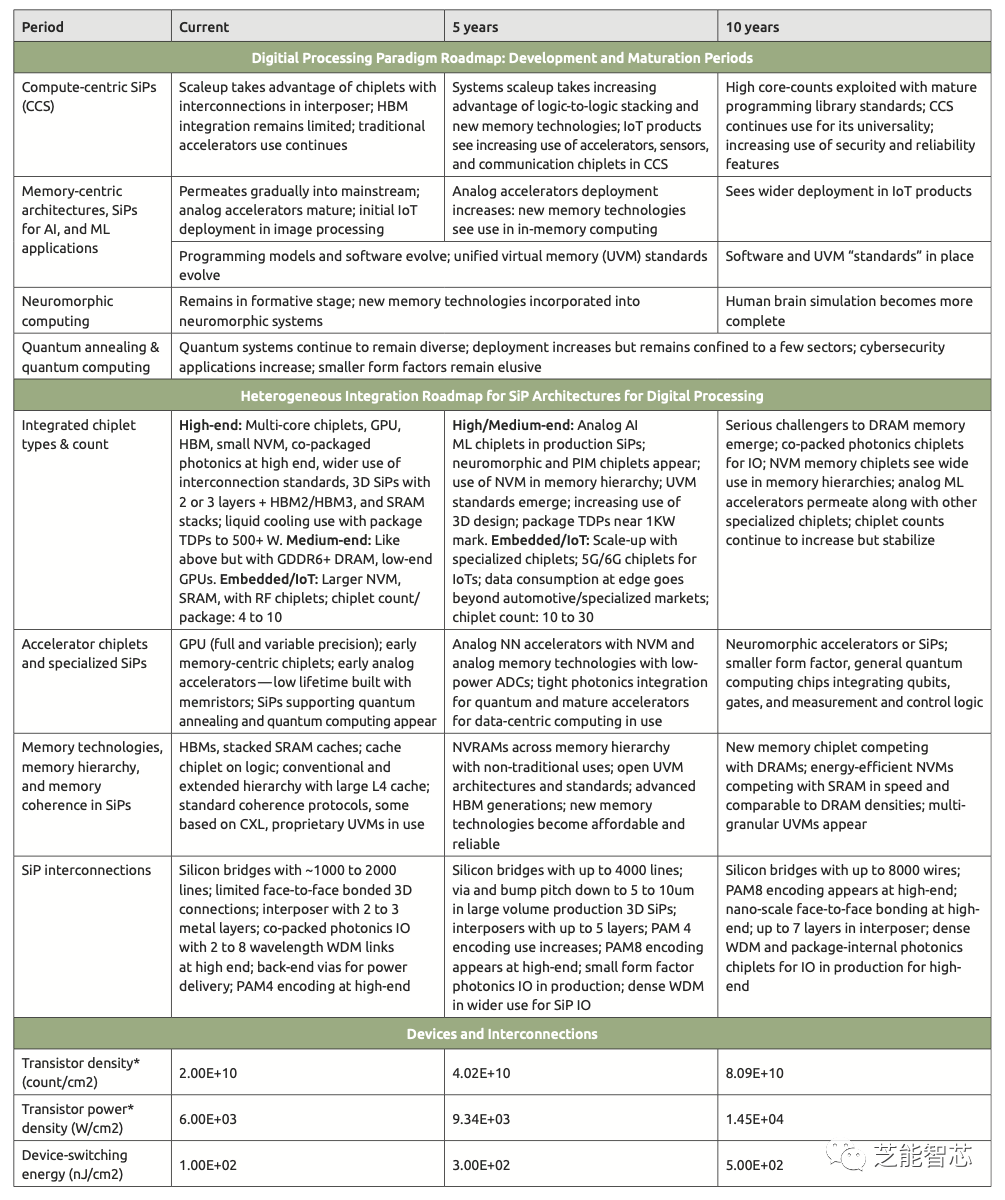

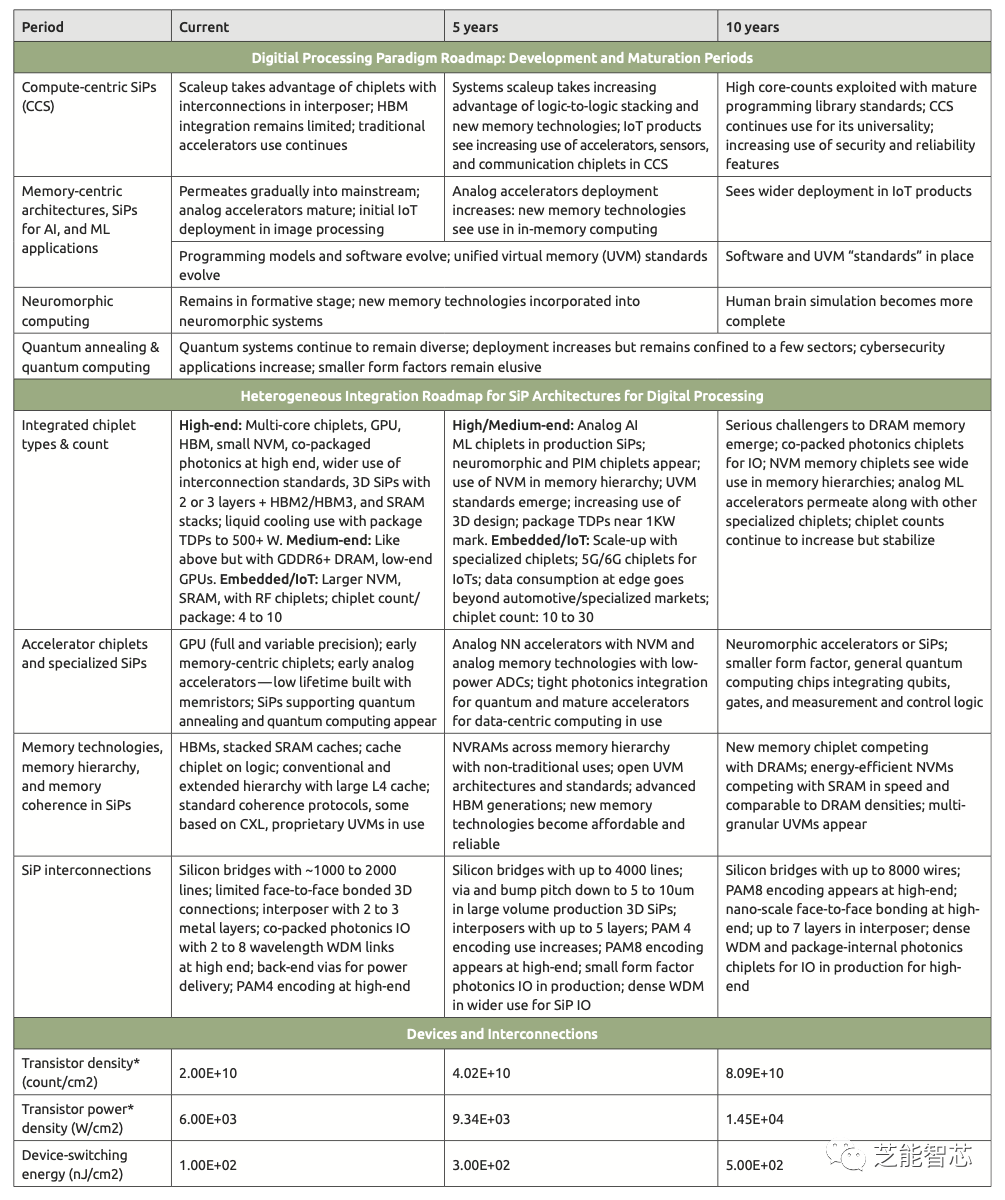

1)基于计算为中心的系统集成(CCS)EuTednc

利用在晶片上具有互联连接的芯片片(chiplets);高带宽内存(HBM)集成仍然受到限制;传统加速器的使用持续增加。EuTednc

◎ 随着系统规模的扩大,逻辑对逻辑堆叠和新的内存技术得到了越来越多的应用;在CCS中,物联网产品越来越多地使用加速器、传感器和通信芯片片。EuTednc

◎ 成熟的编程库标准被用来充分发挥高核心数的优势;CCS由于其通用性继续被使用;安全性和可靠性特性的应用也在增加。

2)以内存为中心的架构,用于人工智能和机器学习应用的系统集成(SiPs)EuTednc

◎ 内存为中心的架构逐渐渗透到主流市场;编程模型和软件不断发展;统一虚拟内存(UVM)标准不断完善。

◎ 模拟加速器技术成熟;模拟加速器的应用范围扩大:初步在物联网中应用于图像处理EuTednc

◎ 在物联网产品中的应用范围扩大。软件和UVM的“标准”已经制定。

3)集成芯片片的类型和数量EuTednc

◎ 高端:多核心芯片片、图形处理单元(GPU)、高带宽内存(HBM)、小型非易失性内存(NVM)、在高端使用共封装光子器件、更广泛地使用互连标准、带有2或3层3D SiPs + HBM2/HBM3和SRAM叠层;使用液冷技术,功耗上限提高至500瓦以上。

◎ 中端:类似于高端配置,但使用GDDR6+ DRAM,低端GPU。

嵌入式/IoT:较大的非易失性内存(NVM)、SRAM,搭配射频(RF)芯片片;每个封装中的芯片片数量:4至10个。EuTednc

◎ 高/中端:模拟人工智能(AI)和机器学习(ML)芯片片在生产中的SiPs中广泛应用;神经形态和处理器内存(PIM)芯片片开始出现;在内存层次结构中使用非易失性内存(NVM);统一虚拟内存(UVM)标准开始出现;3D设计的使用增加;封装功耗上限接近1千瓦。EuTednc

◎ 嵌入式/IoT:使用专用芯片片进行扩展;为物联网设计的5G/6G芯片片;边缘数据处理需求超越汽车/专业市场;每个封装中的芯片片数量:10至30个。

DRAM内存的严峻挑战者出现;具有共封装光子学芯片片的输入/输出解决方案;内存层次结构中广泛使用非易失性内存(NVM)芯片片;模拟ML加速器和其他专用芯片片逐渐渗透;芯片片数量继续增加但趋于稳定。

4)加速器芯片片和专用系统集成(SiPs)EuTednc

◎ GPU(全精度和可变精度);早期的以内存为中心的芯片片;早期的模拟加速器。低寿命的构建,使用忆阻器;支持量子退火和量子计算的SiPs开始出现。

◎ 带有NVM和模拟存储技术以及低功耗ADC的模拟神经网络(NN)加速器;为量子计算和数据中心计算中的成熟加速器提供紧密的光子学集成。EuTednc

◎ 神经形态加速器或SiPs;较小的尺寸,集成了量子比特、门电路和测量与控制逻辑的通用量子计算芯片。

5)内存技术,内存层次和内存一致性在SiPs中的应用EuTednc

◎ HBMs,叠加的SRAM高速缓存;逻辑上的缓存芯片片;带有大型L4缓存的传统和扩展层次结构;标准的一致性协议,其中一些基于CXL,使用专有的UVM。

◎ 在内存层次结构中使用NVRAM,用于非传统的用途;开放的UVM架构和标准;先进的HBM技术;新的内存技术变得更加经济实惠和可靠。

◎ 新的内存芯片片与DRAM竞争;高效能NVM与SRAM竞争速度,并且具有与DRAM相媲美的密度;出现多颗粒度的UVM。

6)SiP的互连技术:EuTednc

◎ 硅桥,具有大约1000到2000条线;有限的面对面粘合的3D连接;带有2到3个金属层的中间层;高端配置下,共封装的光子学IO具有2到8个波长的波分复用(WDM)链路;用于电力传递的后端通孔;高端配置下使用PAM4编码。

◎ 具有最多4000条线的硅桥;大规模生产的3D SiPs中通孔和翘边间距减小至5到10微米;中间层最多5层;高端配置下PAM4编码的使用增加;高端配置下出现PAM8编码;生产中使用小尺寸光子学IO;更广泛地用于SiP IO的密集WDM。

◎ 最多8000条线的硅桥;高端配置下出现PAM8编码;高端配置下纳米级面对面粘接;中间层最多7层;用于高端产品的密集WDM和封装内部光子学芯片片的IO正在生产中。

EuTednc

EuTednc

责编:Ricardo

最前沿的电子设计资讯

最前沿的电子设计资讯