光信号在光纤中的传输损耗为0.2dB/km,而RF电缆在50GHz信号速率下的典型传输损耗为5dB/m。因此光互联独占鳌头,成为长距离信号传输的唯一方案。而电信号互联的距离通常在1m以下,如下图所示。

(图片来自https://community.cadence.com/cadence_blogs_8/b/breakfast-bytes/posts/photonics-keynote)

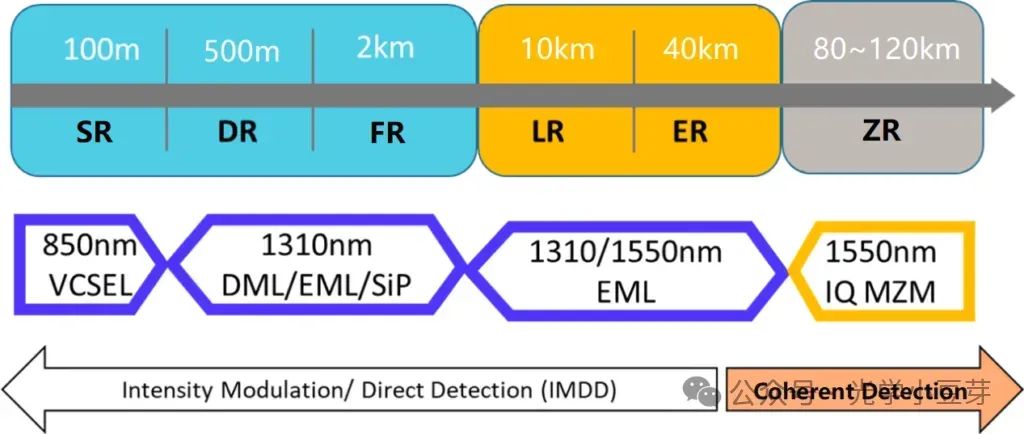

在数据中心内,根据不同距离的连接需求,可插拔光模块可以分为SR(short range)、DR(data center range)、FR(far range)、LR(long range)、ER(extended range)、ZR(extreme range)等,具体的传输距离与采用的光学方案如下图所示。

(图片来自https://www.fibermall.com/blog/what-is-short-range-optical-communication.htm)

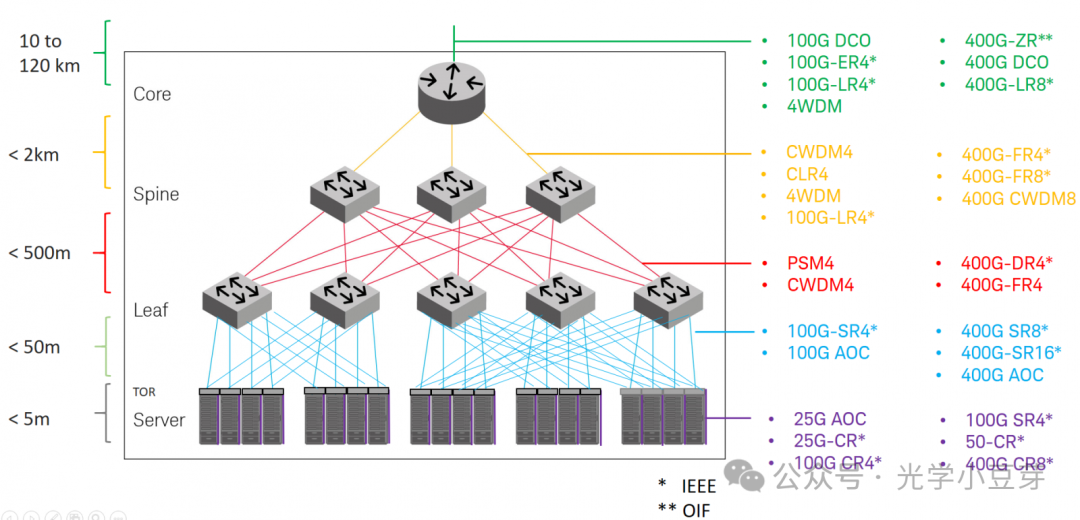

此时光模块主要连接的是服务器和交换机,互联场景包括数据中心之间的互联、数据中心内Core-Spine层的互联、Spine层与Leaf层的互联、Leaf层与TOR的互联、TOR与服务器之间的互联,互联距离从几十公里到几米,如下图所示。

(图片来自https://www.keysight.com/de/de/products/photonic-products/optical-transceiver-test-solutions.html)

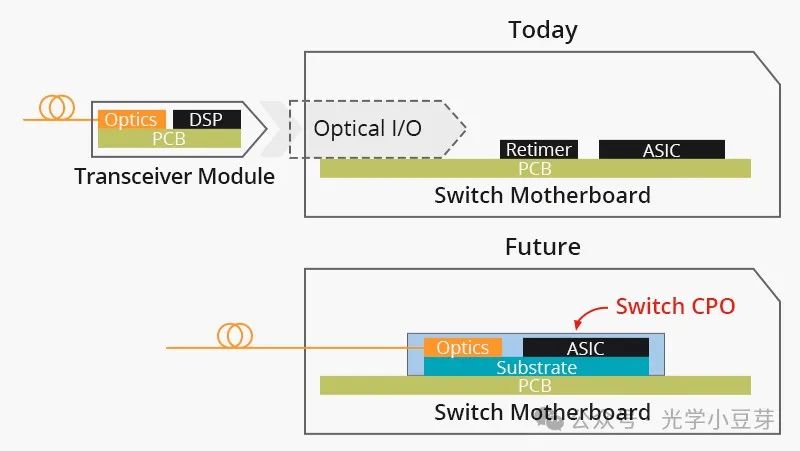

上述的光互联,主要是将switch芯片中的电信号,在PCB板上传递到可插拔光模块,借助光电转换,将高速信号转换到光域,再通过光纤,传递到另一处的switch或者server。高速电信号在PCB上会经过一段较长的走线。为了进一步降低功耗,提高带宽密度,Co-packaged optics的概念应运而生,其主要思想是将光引擎与switch芯片封装在同一个基板上,缩短两者间的电互联距离,降低功耗,提高信号质量(signal integrity),如下图所示。

(图片来自https://community.fs.com/article/a-comprehensive-overview-of-co-packaged-optics.html)

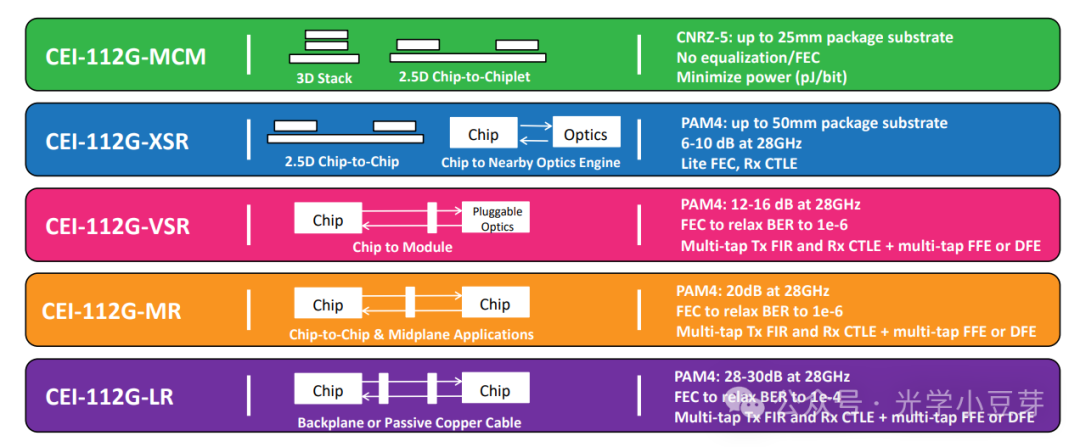

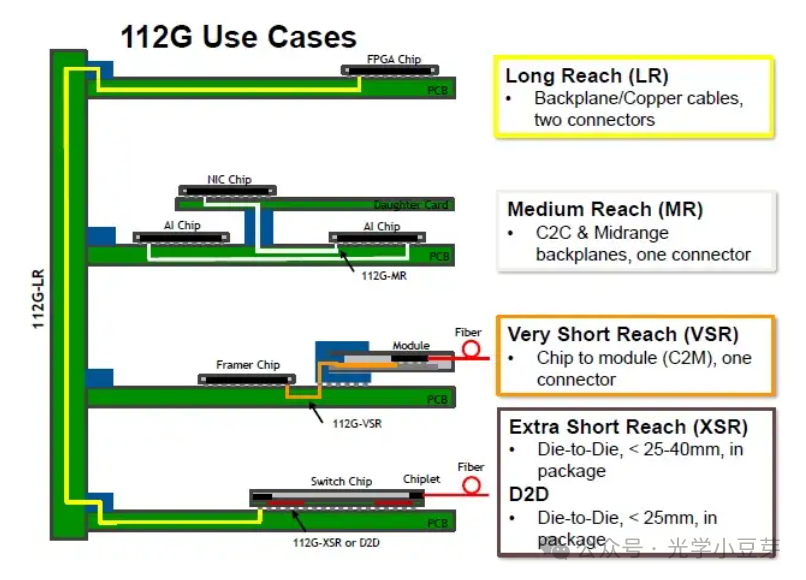

与光互连类似,在substrate/PCB上的高速电信号互联,根据传输距离的不同,也可以分为MCM/XSR/VSR/MR/LR等。针对112Gbps的情况, 电IO的标准有以下几种,

(图片来自https://www.oiforum.com/wp-content/uploads/00311c-OIF-112G-OFC-slides_ofc20_presentation.pdf)

具体来说MCM针对的是2.5D chip to chiplet/3D封装的情况,互联最长距离为25mm。XSR针对的是2.5D chip to chip互联的情况,以及chip到光引擎互联的情况,互联距离最大可以到50mm,链路损耗为6-10dB,CPO模块与switch芯片互联即属于这一情况。VSR针对的是chip to module的信号互联,互联距离可以达到200mm,VSR针对的即是可插拔光模块的场景, 链路损耗为12-16dB。MR针对的是同一板卡上chip to chip以及中板的应用场景,互联距离小于500mm, 链路损耗为20dB。LR针对的是背板之间互联的场景,互联距离可以达到1000mm,链路损耗为28-30dB。这几种电IO的应用场景,如下图所示。

(图片来自https://semiwiki.com/eda/cadence/315096-clocking-for-high-speed-serdes/)

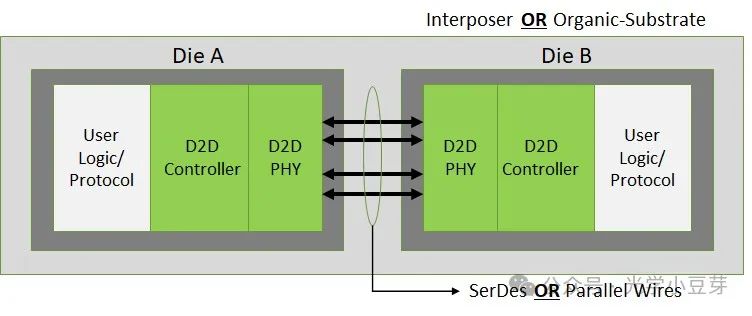

上述的电学IO标准主要针对的是高速电信号传递的情况,采用的是串口数据传输方案。由于在SerDes上带来的开销,相同带宽条件下,并口数据传输在功耗与延迟上有一定的优势。并口数据传输有望应用在die to die(D2D)的信号互联上,单个链路的带宽不大,但是通过增加IO接口的数目,也可以满足D2D高带宽互联的需求。Intel联合多家公司,针对chiplet互联的场景,推出了UCIe互联协议,引起了业界的广泛关注。

(图片来自https://awavesemi.com/silicon-ip/subsystems/die-to-die-ip-subsystem/)

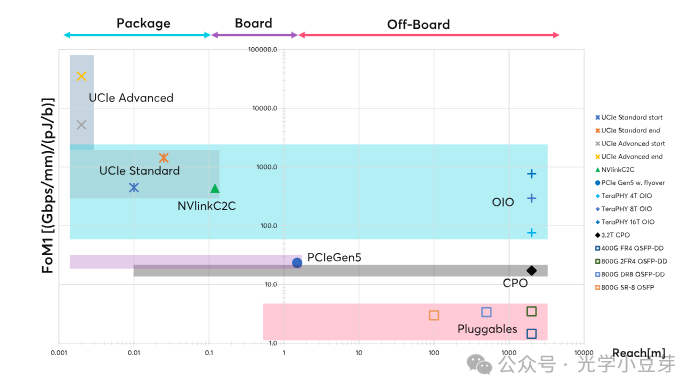

Ayar Labs比较过不同距离下电互联、光互连的带宽密度功耗比,如下图所示。在Off board互联的情况,光互连已经占据主导地位。而在package level互联的情况,CPO与Optical IO也扮演了重要的角色。各种尺度下信号互联的努力目标是提高带宽密度,降低功耗,减小延迟。Ayar Labs的TeraPHY功耗在5pJ/bit以下,NVLink C2C的功耗已经可以做到1.3pJ/bit,UCIe的功耗可以低至0.5pJ/bit以下。光互连和电互联是紧密联系、互相补充的,所谓的"光进铜退",可能只是一个美好的愿景,两者会长期共存,负责不同尺度下的信号互联。计算与存储芯片的高速电信号必须先在package上进行一段距离的传输,再通过光学IO互联到更远的节点处。AIGC的爆发,导致芯片间的互联需求更加重要。长远看,电芯片与光引擎的距离会越来越短,联系会愈加紧密。

(图片来自In-Package Optical I/O Versus Co-packaged Optics | Ayar Labs)

文章中如果有任何错误和不严谨之处,还望大家不吝指出,欢迎大家留言讨论。

最前沿的电子设计资讯

最前沿的电子设计资讯