开关电源是以功率MOS为核心的电能变换器,除了芯片自身的参数会对电能质量产生较大影响外,PCB的设计也是非常重要。

今天,我们将以简单的Buck电路为例,从不同的角度出发,和大家分享一下关于开关侧PCB铺铜的一些设计心得。

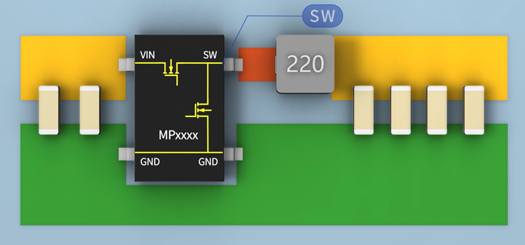

首先,开关侧,也就是我们常说的SW,是Buck电路中非常关键的位置,它是输入回路和输出回路的交点,同时也是桥臂功率MOS直接相连的地方。

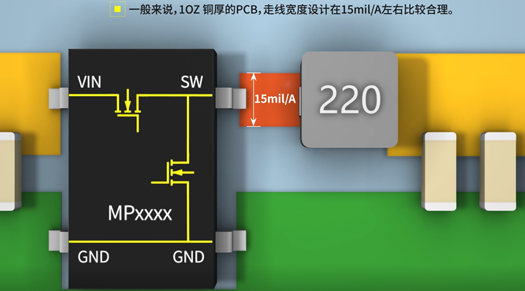

一般来说,和功率MOS相连的信号,PCB的铺铜面积都要尽可能设计得大一些,主要是两方面的考量:

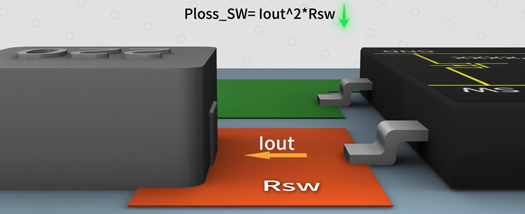

一方面是功率回路需要走较大的电流,在相同距离上,增加铺铜宽度可以增大走线的通流能力,降低路径损耗。

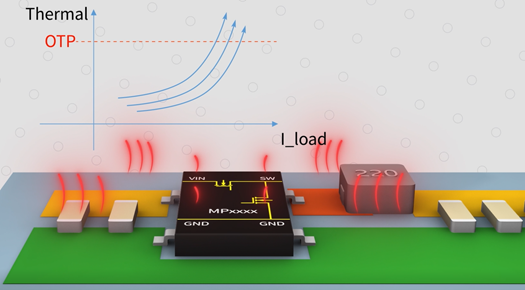

另一方面,和功率MOS直接相连的铺铜,也承担着器件散热的角色。我们知道,散热能力往往会成为电源芯片输出能力的瓶颈。由于芯片pin脚的导热性较好,芯片内核到PCB的热阻往往会小于到封装表面的热阻,这也就意味着芯片大部分热是通过芯片pin脚导入PCB后耗散的,那增加SW的铺铜面积,对于Buck芯片的散热能力,也会有一定程度的提升。

但是,这是否就意味着SW的铺铜越大越好呢?

答案是否定的。

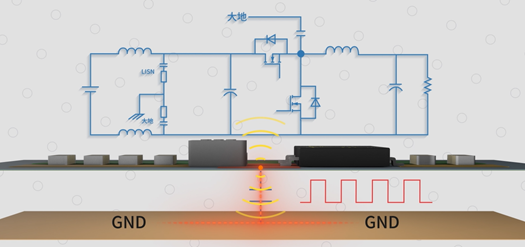

如果从噪声维度去看,SW承接着Buck 拓扑的输入回路和输出回路,随着MOS的开关切换,SW处的电压也会产生周期性的脉冲变化。同时,SW的电流也随着MOS的高频切换,呈现规律性的波动。

当SW铺铜面积变大,那么对参考地的寄生电容也会随之增大,高频电压波动带来的噪声更容易通过寄生电容耦合到参考地, 从而影响其它采样信号的识别。

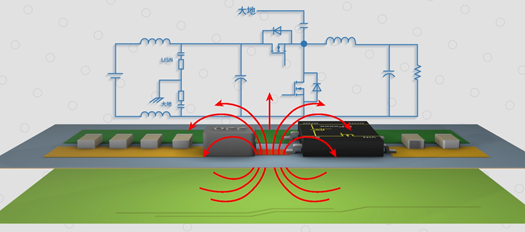

同时,变化的电流会在空间产生变化的磁场,当磁导线穿过闭合线圈时,则会感应出电压噪声,对附近的信号产生一定的影响。随着铺铜面积的增加,干扰的辐射范围也就越广。

所以,为了尽可能减小对周边信号的影响,我们希望SW的铺铜面积越小越好。

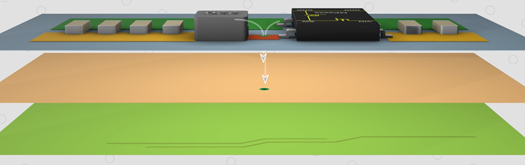

另外,我们也不建议在SW处打过孔。

在实际应用中,为了减小电源噪声对信号链的影响,我们会在电源层下面加一层完整的GND作为噪声屏蔽层。一旦SW处增加了过孔,就破环了屏蔽层的完整性,噪声就会沿着过孔干扰到其它层的信号传输。

那么,如何解决上述的矛盾呢?

最前沿的电子设计资讯

最前沿的电子设计资讯