大家在测试电源电路时,有时会碰到输出电压异常、输出纹波过大等情况,此时通常会排查 SW 信号来判断电路工作是否正常,异常状况下 SW 波形会呈现大小波现象。

今天我们就来一起看下,SW 出现大小波的常见原因有哪些?应该排查什么?

SW 大小波现象简介

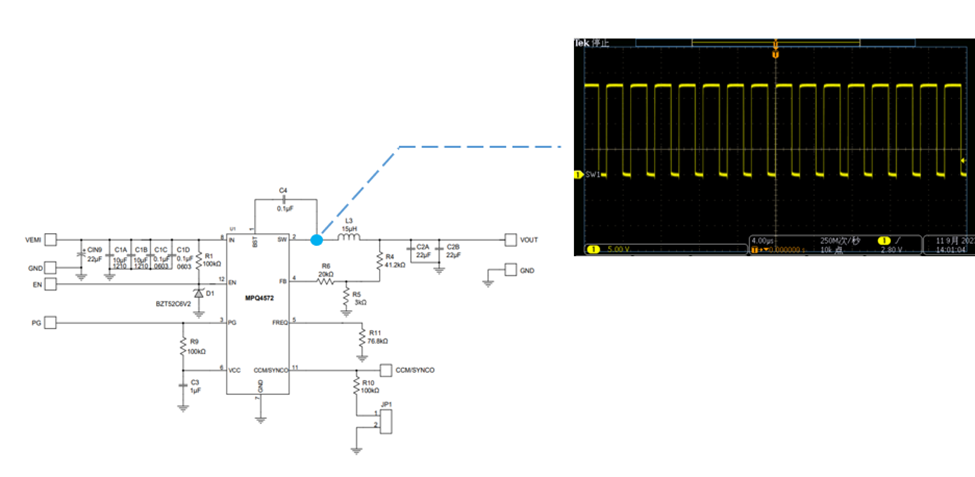

SW 代表 BUCK 电路中的开关节点。在标准工作条件下,SW 点的波形表现为固定频率的方波。

图1:正常工况下的SW波形

然而,在某些异常情况下,SW 波形会呈现大小波状态。通常伴随着输出电压不稳定、效率降低、芯片异常发热,以及噪声纹波增大等问题。

因此,在开关电源设计中,通常需要采取措施来控制 SW 节点上的电压波动,以确保电源的稳定性和可靠性。

图2:SW大小波

SW 大小波现象的原因分析

电路中 SW 出现大小波可能有以下几种原因:

负载变化

输入电压不稳定

环路控制和补偿设计不当

PCB 布局布线不合理

本文将从原理图设计和 PCB 设计两个方面,分析 SW 出现大小波的原因,并介绍对应的解决办法。

在原理图设计方面,我们从控制模式展开分析。

在 PCB 设计方面,从对 SW 影响最大的输出电压采样走线和 FB 走线展开分析。

原理图设计

在控制模式方面,目前常用的有峰值电流模式控制和 COT 控制。

峰值电流模式下的 SW 异常状态我们通过 MPQ4572 举例分析:

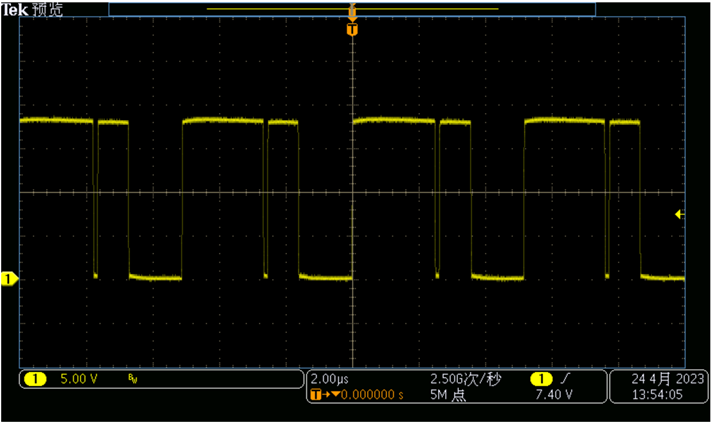

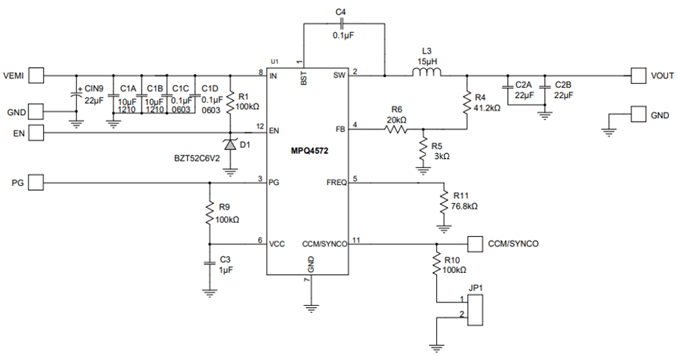

图3:MPQ4572 参考设计

MPQ4572 是一款支持 4.5V 到 60V 的宽输入电压范围,持续输出电流 2A,采用峰值电流控制模式的降压芯片。

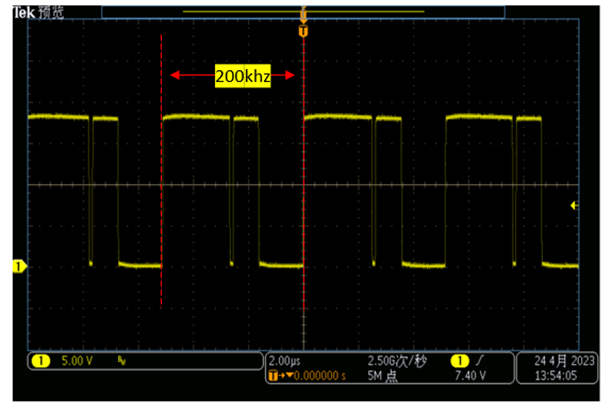

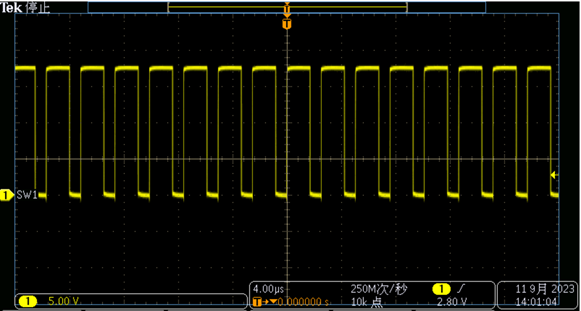

测试该芯片,设置开关频率为 400Khz,当 Vin=18V,Vout=12V,带载 1A 时,SW 出现了大小波,为周期性不规则波形,变化周期为 200khz,刚好是开关频率的一半,这种现象可能是由次谐波振荡引起的。

图4:SW 大小波

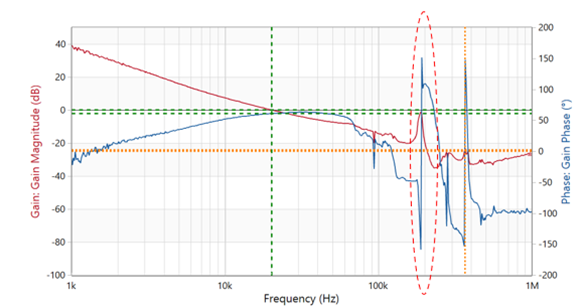

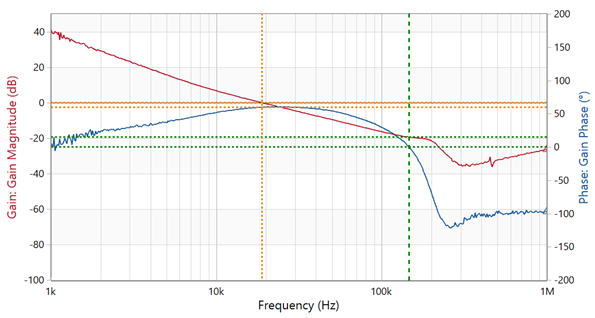

测试当前的环路波形,根据 bode 图可以看到在 200khz 时,增益曲线出现尖峰,相位曲线翻转,可以判断是发生了次谐波振荡。当输入电压升高到 25V 以上时,SW 波形恢复正常。

图5:环路测试

计算两种输入下的占空比分别为 :

Vin=18V,Vout=12V:D=66.7%>50%,

Vin=25V,Vout=12V:D=48%<50%,

已知在峰值电流模式下,当占空比大于 50% 时,系统可能会变得不稳定,出现次谐波振荡,SW 呈现大小波。

为了抑制这种振荡,通常会在控制回路中注入斜坡补偿信号。但 MPQ4572 芯片的内部已经设计有斜坡补偿机制,为什么还是会出现次谐波振荡的问题呢?

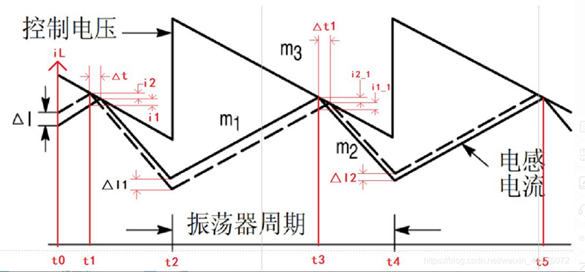

图6:斜坡补偿

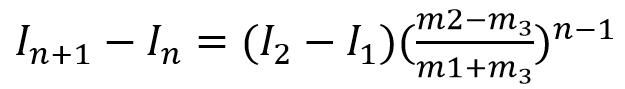

在注入斜坡信号后,扰动量的公式为:

为了保证电路工作稳定,要让扰动量收敛。注入的斜坡斜率 m3 要大于 0.5 倍 m2 才能使该式收敛。如果 m3 小于 0.5 倍 m2,即使注入了斜坡信号,也无法解决次谐波振荡问题。

芯片内部注入的斜坡信号斜率通常是未知的固定值,也就是说 m3 是固定的,那么我们可以通过增加电感感量减小 m2 来保证 m3>0.5 倍 m2 成立。当电感感量由 15uh 修改为 33uh 后,SW 波形恢复正常。

图7:正常 SW 波形

测试此时的 bode 图,200khz 时的增益曲线尖峰消失,环路稳定。

图8:33uh 环路测试

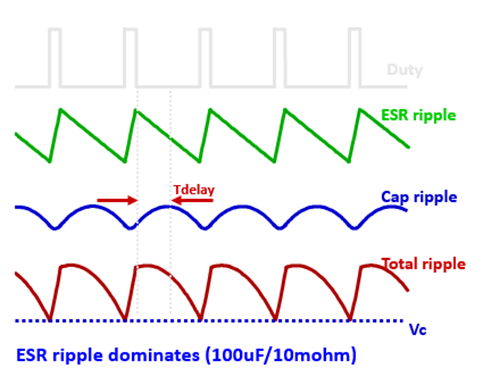

COT 是通过比较 Vref 与 FB 管脚的电压来实现恒压控制,理想的 FB 电压与电感电流同相位。

FB 采样的输出电压纹波信号由电容纹波与 ESR 的纹波组成,电容纹波相较电感电流纹波有 90 度的延迟,当输出纹波主要由输出电容决定时,电路相位滞后,FB 信号非线性,会导致次谐波振荡,SW 出现大小波。

在这种模式下,我们有三种方法可以用来抑制次谐波:

使用 ESR 足够大的电容

ESR 越大,总的电路相位延迟越小,纹波接近线性,可以有效抑制次谐波振荡。

图9:ESR 纹波占主导

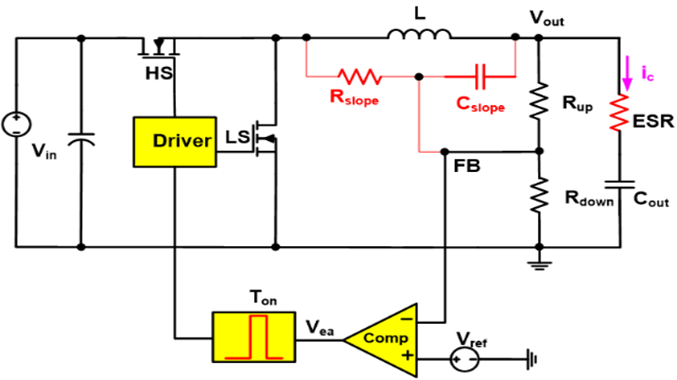

注入斜坡补偿

当为了效率及输出纹波幅度考虑,需要选择 ESR 比较小的电容时,我们可以选择注入斜坡补偿。通过外部的 RC 补偿给 FB 管脚注入斜坡信号,由 Rslope 引入电感纹波,Cslope 提高相位,整体相位提升,可以抑制次谐波。

图10:斜坡补偿

具体参数如何计算可参考:MPS官网-设计-应用说明-通用-Designing a Stable COT Converter for a Desired Load and Line Regulation 的设计案例 。

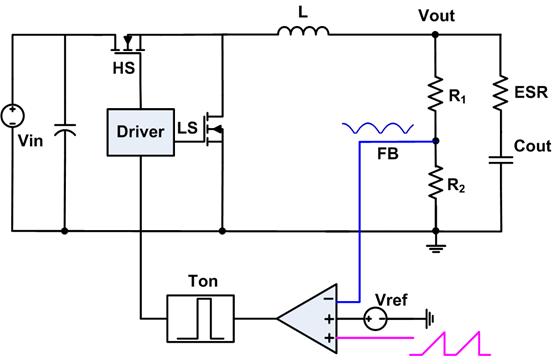

设置 Ramp

Ramp 的相位与电感纹波电流相位一致,部分芯片的 Ramp 可以通过 PMBUS 配置,Ramp 越大,系统越稳定,Ramp 越小,动态响应越快,实际应用中需要平衡稳态性能和动态性能。

图11:设置 Ramp

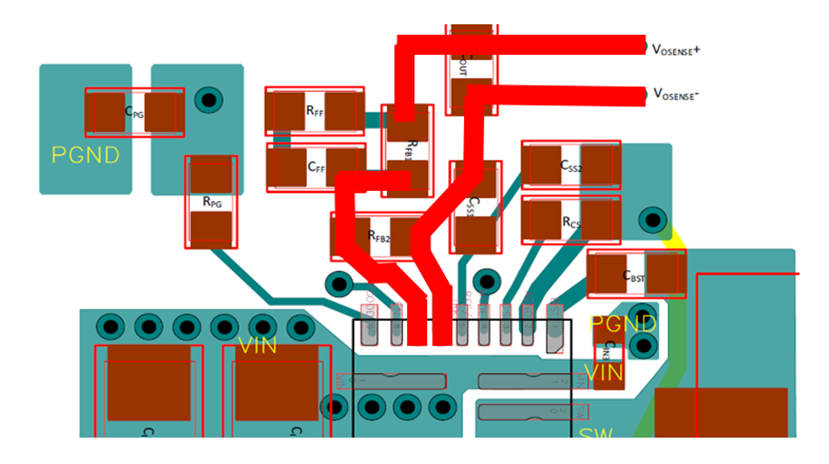

PCB 设计

在 PCB 设计上,规避 SW 振荡的要点包括:

1. 输出电压采样走线应尽量短、直,避免干扰。

2. FB 管脚比较敏感,应远离噪声源,如 SW 点、电感等。

3. FB 分压电阻要靠近管脚放置并确保 FB 走线短直。

总结

峰值电流模式控制下,确保斜坡注入信号的有效性至关重要。

在 COT 控制模式下,当输出纹波由 ESR 主导时,电路稳定;由电容纹波主导时,可能出现次谐波振荡。此时,我们可以通过选用 ESR 较大的电容、增加外部 RC 补偿或内部配置 RAMP 来解决问题。

最后,良好的 PCB 设计也是确保电源稳定性的关键。

END

最前沿的电子设计资讯

最前沿的电子设计资讯