当高速先生问DeepSeek如何优化112Gbps信号过孔阻抗时,得到的答案提纲是这样的:

不得不说,DeepSeek考虑还是比较全面的,从设计到板材,从仿真到测试,面面俱到。

不过,DeepSeek的答案只是一个参考,针对这个具体问题的回答,部分参数还有待商榷(鉴于此,上图仅给出了答案要点,并未列出全部内容)。或许,正如网络上对当前AI工具的评价:“AI工具不是魔法棒,只是使用者能力的放大器”。

言归正传,本文就以Layout攻城狮最关心的过孔反焊盘优化为切入点,展开说说。

有同学会问,为啥专讲过孔反焊盘?

因为越来越多开始接触112Gbps信号设计的Layout攻城狮气愤的发现:同一个BGA(或者连接器),过孔的反焊盘优化方案可能会随走线层面的改变而变化,走线层面越多,对应的优化方案种类也越多,以前的信号反焊盘哪来这么多名堂?!

SI攻城狮也很烦躁:要是能一种方案全部搞定,谁愿意建那么多仿真模型?!

其实,要把这事说清楚,还是得聊过孔阻抗。

高速先生前不久写过一篇文章《不是!让高速先生给个过孔优化方案就那么难吗?》,介绍了差分信号过孔阻抗的影响因素。本案例为了简化问题,减少了变量,选择同一BGA的差分信号过孔作为研究对象,保证了板材、层叠、过孔尺寸、差分过孔及相邻地过孔的分布条件相同,不同走线层面改变的只是过孔长度。同时,选择长、短两种过孔作为仿真对象,差分信号走线特征阻抗控制93欧姆。

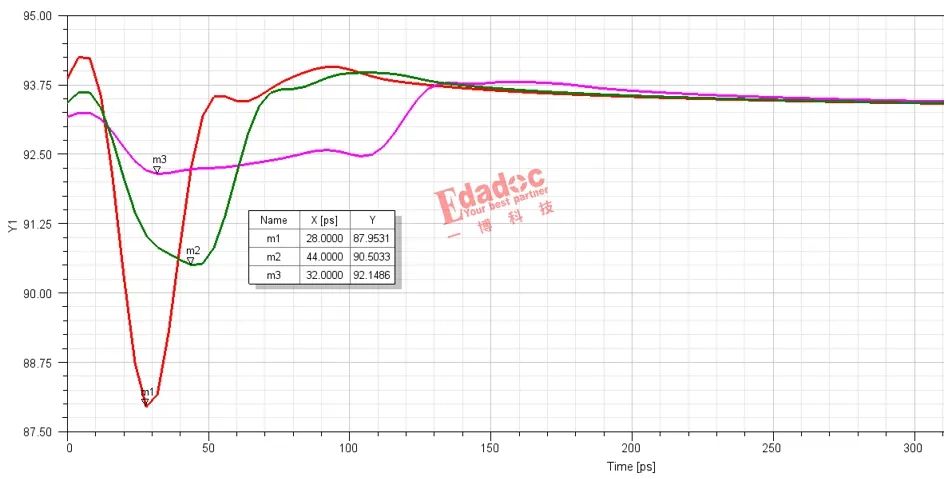

一方面,相同过孔对于不同速率的信号所表现的阻抗是不一样的。速率差异越大,阻抗波动就越明显。

比如,对于本案例中相同的短过孔,112Gbps信号的过孔阻抗仅87.9欧姆,56Gbps信号的过孔阻抗90.5欧姆,10Gbps信号阻抗可以达到92.1欧姆。

乍一看好像很神奇,细一想也没那么玄:关键就在于过孔本身存在寄生电容和寄生电感,容抗和感抗都随频率变化,因此过孔的阻抗也是一个频变量,对于不同基频的信号表现出不同的阻抗也就不足为奇了。

另一方面,不同走线层面的过孔对于同一信号速率的阻抗也是不一样的,只不过信号速率没那么高的时候,阻抗差异相对较小,所以可以采用同一种反焊盘优化方案,这也是Layout攻城狮熟悉的处理方式。

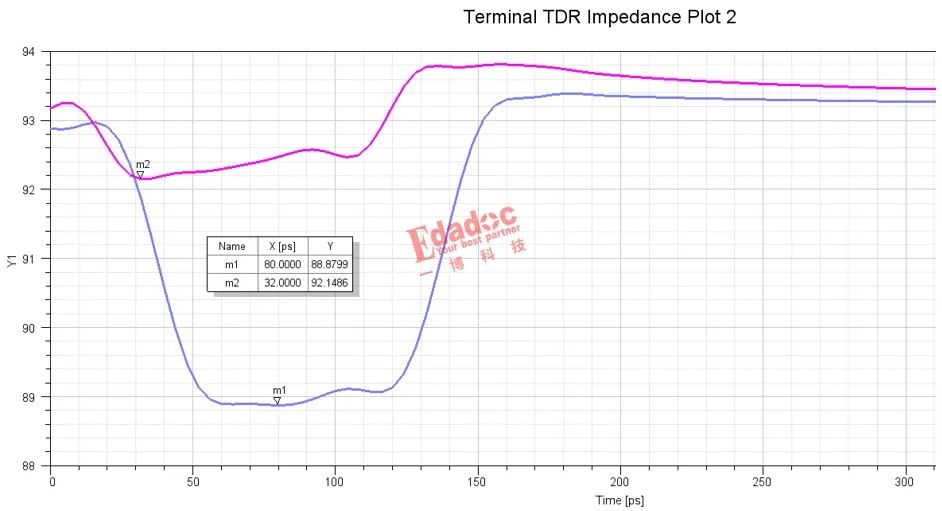

本案例中长、短两种过孔采用同一种反焊盘方案时,对于10Gbps信号,短过孔阻抗92.1欧姆,长过孔阻抗88.8欧姆,阻抗差异只有3.3欧姆:

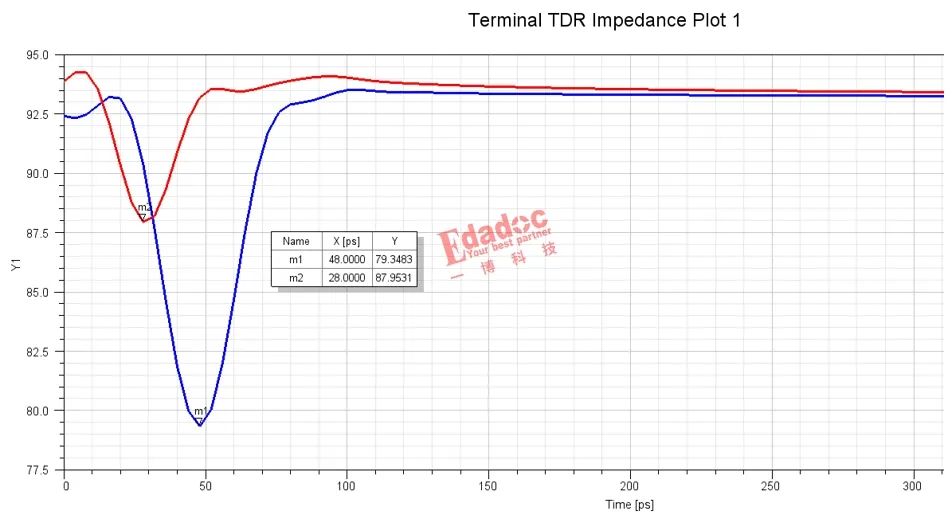

同样的情况,对于112Gbps信号,短过孔阻抗87.9欧姆,长过孔阻抗79.3欧姆,阻抗差异增加至8.6欧姆。一种反焊盘优化方案显然无法同时满足需求。

因此,对于112Gbps信号,有时真不是SI攻城狮花样多,不同长度的过孔确实需要进行针对性的反焊盘优化,方案大概率会随走线层面的改变而变化。

需要说明的是,本案例中的长、短过孔都是容性占主导地位,阻抗偏低。对于一些板厚较大的单板,即便信号速率不是特别高,由于过孔长度差异悬殊,短孔呈容性,阻抗偏低,长孔呈感性,阻抗偏高,相同反焊盘的长孔和短孔,阻抗差异也会大到难以接受。高速先生在另外一篇文章里分享过感性长孔的阻抗特点《钻刀无忌,过孔莫愁》,在那个案例里,信号速率只有25Gbps,所以说,112Gbps也不是信号速率高低的绝对分界线。

随着信号速率和单板复杂度越来越高,想要一举多得用一种方案应对多种情况的可能性越来越小,幸运的是,万变不离其宗,优化的思路不会变。反焊盘方案能否兼容最好通过仿真验证,如果非要高速先生给出答案,那只能是:It depends!

最前沿的电子设计资讯

最前沿的电子设计资讯