大型系统正在自己的模拟前端使用更多更快的通道,设计者必须为其选择CMOS、LVDS亦或CML输出。必须了解这些输出的主要特性、性能折衷,以及布局要求。

要点

1.高端仪表促进了更快的ADC速度和更多的通道数与密度,设计者必须评估转换器的输出格式,以及基本的转换性能。

2.主要的输出选项是CMOS(互补金属氧化物半导体)、LVDS(低压差分信令),以及CML(电流模式逻辑)。

3.要考虑的问题包括:功耗、瞬变、数据与时钟的变形,以及对噪声的抑制能力。

4.对于布局的考虑也是转换输出选择中的一个方面,尤其当采用LVDS技术时。

当设计者有多种ADC选择时,他们必须考虑采用哪种类型的数字数据输出:CMOS(互补金属氧化物半导体)、LVDS(低压差分信令),还是CML(电流模式逻辑)。ADC中所采用的每种数字输出类型都各有优缺点,设计者应结合自己的应用来考虑。这些因素取决于ADC的采样速率与分辨率、输出数据速率,以及系统设计的功率要求,等等。

CMOS驱动器

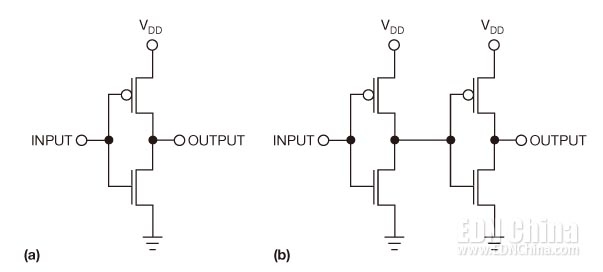

在采样速率低于200M采样/秒的ADC中,常见的是CMOS数字输出。典型的CMOS驱动器包括一个NMOS管和一个PMOS管(它们的漏极相互连接)、电源电压VDD和地(图1a)。这个结构会使输出反相。另外,也可以采用一种背对背的结构,避免输出反相(图1b)。

图1,一个典型CMOS数字输出驱动器可以是反相结构(a),或非反相结构(b)。

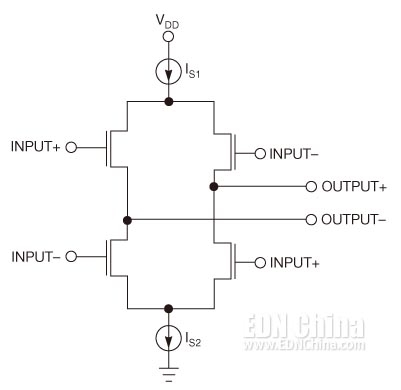

图2,LVDS输出驱动器提供受控的输入与输出阻抗。

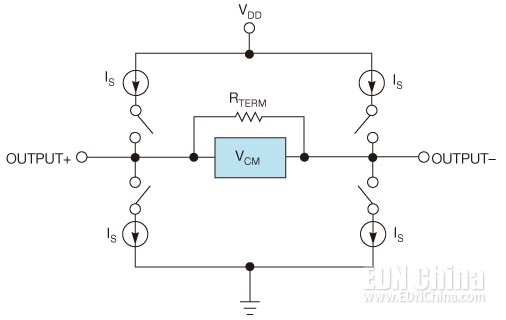

图3,CML输出驱动器作为电路输入,驱动着电流源的开关,从而将两个输出端子驱动到适当的逻辑值。

-

微信扫一扫

一键转发 -

最前沿的电子设计资讯

最前沿的电子设计资讯

请关注“电子技术设计微信公众号”

- 用“老古董”电荷泵将电压减半,使电流“效率”加倍 本文展示了一个Vout=Vin/2、Iout=Iin*2的示例泵,它是围绕着古老的xx4053系列三重CMOS SPDT开关构建的……

- SynQor®发布适用于MIL-STD-1275的军用级直流输出功率 SynQor ® 是一家领先的电源转换解决方案供应商; 近期宣布为直流输出浅机架军用级电源调节器系列推出一款新的“恒定电流过载保护”型号。该型号满足MIL-STD-1275D的规定,可允许将输出直接连接到28V车载电力系统一起使用的铅酸电池的端子……

- 帧指针是落后技术?谷歌用它将Go语言跟踪器开销降至1% 近日,谷歌Go语言开发团队发布消息称,改进了其运行环境的跟踪器功能,可解决跟踪器开销过大的问题,将CPU负载降低至1%……

- 我国达成薄膜散热新记录:1m²散热量相当于1万台2kw电热 近日,华北电力大学的研究团队在薄液膜沸腾研究方面取得了突破性进展,成功实现了2074W/cm²的超高热流密度,刷新了国内外目前已知的相关公开纪录,有望进一步提升器件设备散热效果……

- 电源功率密度设计极限再获突破,专家解读背后秘密 功率密度、低EMI、低IQ、低噪声高精度与隔离功能既是未来电源管理芯片发展的五大前沿趋势,也是衡量一家企业的产品性能是否继续享有领导地位的重要指标,5-10年内将不会出现任何改变。

- 苹果最新MacBook Air“翻车”?M3处理器最高飙到114℃ 新款MacBook Air在运行3DMark Wild Life Extreme、CineBench 2024等测试项目时,M3处理器在测试中温度多次达到惊人的114℃,在CPU测试中即使降频后最高温度也有107℃,而机身最高达到了46℃···

- 华为开发颠覆性磁电硬盘MED:功耗比机械硬盘降低90% 按照华为的说法,MED主要定位于档案存储,作为大容量磁盘,第一代磁电硬盘可以在单个机架内实现10PB也就是10000TB的容量,而功耗不到2000W,相比机械硬盘功耗降低90%,而相比磁带存储可以节省 20%的总连接成本···

- 意法半导体新双向电流检测放大器为工业和汽车应用带来 TSC020适用于高低边电流检测,共模电压范围宽达-4V到100V,可用于48V以上的汽车电源系统。高精度内部电路确保输入失调电压在±150µV以内,这有助于大幅减小外部分流电阻器的尺寸,降低耗散功率。优异的低压降检测功能有助于最大限度地减少测量误差。

- Ceva 推出面向 FiRa 2.0 的下一代低功耗超宽带 IP为消 RivieraWaves® UWB IP for FiRa 2.0具有尖端的干扰消除功能,将Ceva从汽车和移动设备市场扩展到智能家居、智能工厂等领域的大批量UWB导航、检测和远程控制用例~

- 兆易创新推出GD32F5系列Cortex®-M33内核MCU,提供工业 GD32F5系列高性能MCU具备显著扩容的存储空间、优异的处理能效和丰富的接口资源,该系列MCU符合系统级IEC61508 SIL2功能安全标准,并且提供完整的软硬件安全方案,能够满足工业市场对高可靠性和高安全性的需求。

- 意法半导体推出灵活多变的同步整流控制器,提高硅基或氮 有助于简化工业电源、便携式设备充电器和交流/直流适配器操作,节省电能~

- ENNOVI推出ENNOVI-CellConnect-Prism,彻底颠覆电池技术 支持实现方形电芯之间的稳固连接,灵活运用于CTM、CTP和CTC等先进的动力电池系统,简化装配流程,并降低材料成本。

- 3月第2周新能源周销量,油车继续低迷 2024年第11周(3月11日-17日),乘用车总销量33.7万辆 ,同比上涨11.4%……

- 2024蓝牙音响市场趋势全解读 在本文中,我爱音频网将对 2023 年的蓝牙音响行业进行市场数据梳理分析,并对全年的技术趋势进行回顾性总结,帮助

- 特斯拉的4680锂离子电池的电特性 特斯拉4680锂离子电池的性能和特性。通过三电极分析、电学和热学特性的表征,上一代的4680并没有达到设计目标

- 智能接口大发展,USB-C十周年回首 USB-C接口自推出以来,带给行业翻天覆地的变化,虽然看似只是简单的接口迭代,牵扯的却是设备连接、充电等重要拓

- 拆解报告:石龙富华35W PoE电源适配器 石龙富华这款PoE电源适配器支持35W输出功率,在机身两侧设有固定孔,可以固定在墙壁或者机架上。适配器采用八字

- YAMAHA雅马哈YH-E700B头戴式降噪耳机拆解 YAMAHA雅马哈YH-E700B头戴式降噪耳机外观上采用了全新设计,能够更好的适应不同头型的舒适佩戴需求。在功能配

- 让电池测试变得简单 早在蜂窝电话诞生之时,各个厂商就开始用电池为手机供电;而随着 21 世纪初期智能手机的问世,蜂窝电话真正迎来

- 拆解报告:罗马仕10000mAh 67W超级快充移动电源 罗马仕这款超级快充移动电源为充电器+充电宝二合一设计,内置的氮化镓充电器支持67W快充输出,移动电源为10000m

- 花了大价钱的激光孔设计性能竟然不如普通通孔? 我们都知道,激光孔的性能不至于那么差,只不过是使用它的方法在这个场景上是真的不对,单纯从PCB设计上来看,你可

- EDIFIER漫步者ComFo Fit开放式耳机拆解 漫步者ComFo Fit开放式耳机支持双MIC ENC通话降噪,能够有效分离与消除环境噪音,提供清晰通话效果;支持游戏模式

- 古老的物理量如何在今天产生新的应用 光的频率和相位作为基本参数,它们支撑着我们对光的波动性的理解。进一步深入研究非线性光学,我们发现了光的行

- NVIDIA发布“封杀令”:CUDA转译将被禁止 英伟达最近发布了一项禁令,不允许在其他GPU上运行CUDA软件。这一举措引发了关于CUDA兼容禁令的讨论,以及对国

- 东芝在其电机控制软件开发套件中新增位置估算控制技术,旨在简化电 现在提供“MCU Motor Studio Ver.3.0”和新的“电机参数调整工具”···

- 意法半导体发布先进的超低功耗STM32微控制器,布局工业、医疗、智 新旗舰产品,超低功耗,物超所值···

- SynQor®发布适用于MIL-STD-1275的军用级直流输出功率调节器(MPC- SynQor ® 是一家领先的电源转换解决方案供应商; 近期宣布为直流输出浅机架军用级电源调节器系列推出一款

- Arteris 扩展面向 Armv9 架构 CPU 的汽车解决方案 Arteris宣布了其与 Arm 持续合作的首批成果,以加速基于最新一代 Arm® 汽车增强型(AE)技术的汽车电子创新

- ENNOVI推出汽车10Gbps+以太网连接器解决方案 采用基于鱼眼端子压接技术的USCAR接口,成为市场上首个定制化以太网连接器解决方案···

- 意法半导体高性能微控制器为智能家居和工业系统新创新扫清障碍 STM32H7R/S微控制器将嵌入式应用性能提高到一个新水平,适合新一代智能工厂、建筑、基础设施和健康监测设备·

- Arm 宣布推出全新汽车技术,可缩短多达两年的人工智能汽车开发周 Arm 控股有限公司今日携手生态系统合作伙伴推出最新的 Arm 汽车增强 (AE) 处理器和虚拟平台,让汽车行业在开

- 康佳特推出aReady.COM新产品家族—aReady. 战略的第一个关键阶 嵌入式和边缘计算技术的领先供应商德国康佳特,推出全新aReady.COM产品家族,这是其创新的aReady. 战略的第一个

- Vishay的新款80 V对称双通道 MOSFET的RDS(ON) 达到业内先进水 节省空间型器件所需PCB空间比PowerPAIR 1212封装分立器件减少50 %,有助于减少元器件数量并简化设计

- 思特威推出1600万像素手机图像传感器新品SC1620CS 思特威推出1600万像素手机图像传感器新品SC1620CS

- 嘉楠基于RISC-V的端侧AIoT SoC采用了芯原的ISP IP和GPU IP 将芯原像素处理IP组合集成到高精度、低延迟的K230芯片中

- Vishay推出升级版TFBS4xx和TFDU4xx系列红外收发器模块,延长链路距 器件符合IrDA®标准,采用内部开发的新型IC和表面发射器芯片技术,可以即插即用的方式替换现有解决方案···